## CSC 252: Computer Organization Fall 2021: Lecture 26

Accelerators

#### Instructor: Alan Beadle

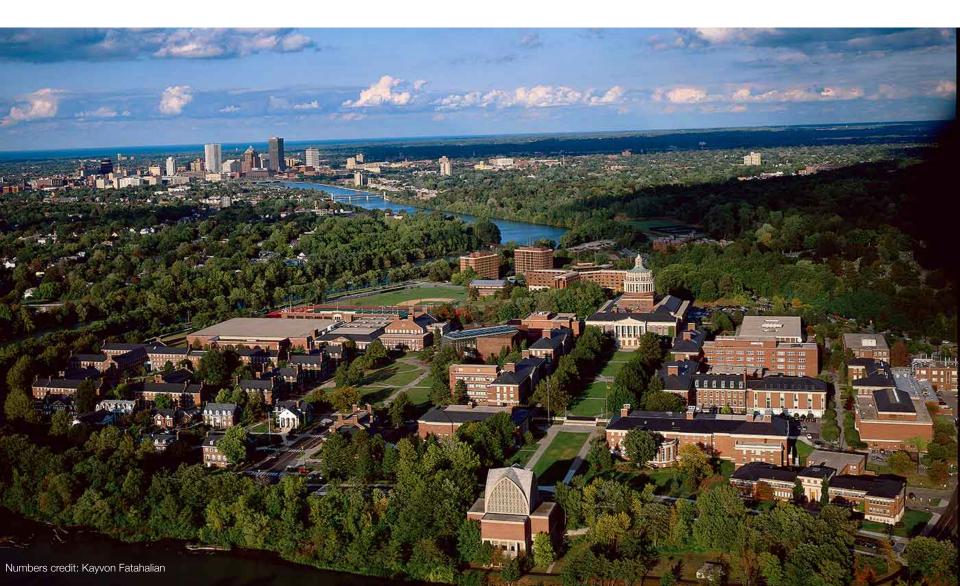

Department of Computer Science University of Rochester

## Announcements

- A5 due Dec 9<sup>th</sup> (day after last lecture)

- Let Abhishek know about slip days

- Next lecture is 100% review

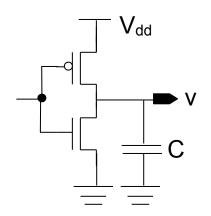

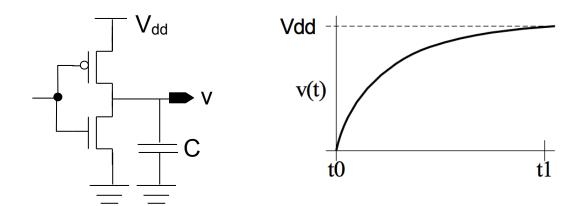

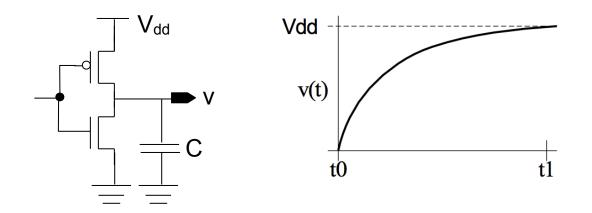

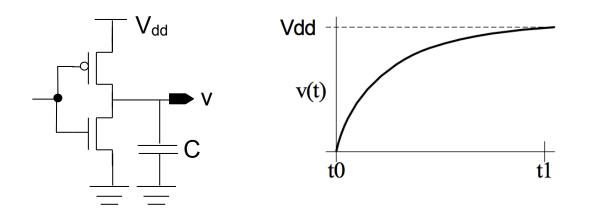

$$E_{sw} = \int_{t_0}^{t_1} P(t)dt = \int_{t_0}^{t_1} (V_{dd} - v) \cdot i(t)dt = \int_{t_0}^{t_1} (V_{dd} - v) \cdot c (dv/dt) dt =$$

$$= cV_{dd} \int_{t_0}^{t_1} dv - c \int_{t_0}^{t_1} v \cdot dv = cV_{dd}^2 - \frac{1}{2}cV_{dd}^2 = \frac{1}{2}cV_{dd}^2 = \frac{1}{2}cV_{dd}^2$$

Energy dissipated for every transition (0->1 or 1->0)

$$E_{sw} = \int_{t_0}^{t_1} P(t)dt = \int_{t_0}^{t_1} (V_{dd} - v) \cdot i(t)dt = \int_{t_0}^{t_1} (V_{dd} - v) \cdot c (dv/dt) dt =$$

$$= cV_{dd} \int_{t_0}^{t_1} dv - c \int_{t_0}^{t_1} v \cdot dv = cV_{dd}^2 - \frac{1}{2}cV_{dd}^2 = \frac{1}{2}cV_{dd}^2$$

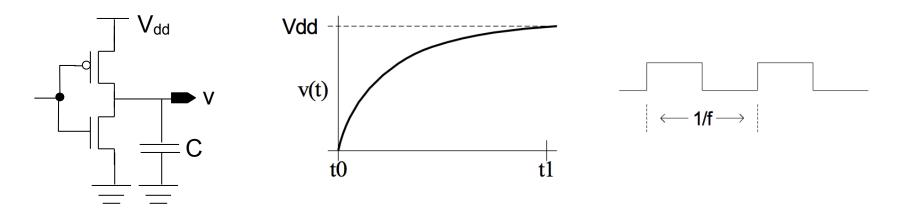

Average dynamic power of a transistor:  $P = a \cdot (E / T) = a \cdot E f = \frac{1}{2} a C V_{dd}^2 f$

a: switch activity factor. No switching, no dynamic power consumption

## $P = k C V^2 f$

## $\mathsf{P} = \mathsf{k} \, \mathsf{C} \, \mathsf{V}^2 \, \mathsf{f}$

• Increasing f requires V to be increased proportionally

- Increasing f requires V to be increased proportionally

- Intuitively: a higher frequency means a shorter cycle time, which means the critical path of your processor needs to be shorter, which requires faster transistors, which you get by increasing the voltage

- Increasing f requires V to be increased proportionally

- Intuitively: a higher frequency means a shorter cycle time, which means the critical path of your processor needs to be shorter, which requires faster transistors, which you get by increasing the voltage

- "Overclocking" just increases the clock speed without increasing voltage => machine might crash (cycle time shorter than the critical path delay)

- Increasing f requires V to be increased proportionally

- Intuitively: a higher frequency means a shorter cycle time, which means the critical path of your processor needs to be shorter, which requires faster transistors, which you get by increasing the voltage

- "Overclocking" just increases the clock speed without increasing voltage => machine might crash (cycle time shorter than the critical path delay)

- Corollary: reducing voltage requires reducing frequency

- Increasing f requires V to be increased proportionally

- Intuitively: a higher frequency means a shorter cycle time, which means the critical path of your processor needs to be shorter, which requires faster transistors, which you get by increasing the voltage

- "Overclocking" just increases the clock speed without increasing voltage => machine might crash (cycle time shorter than the critical path delay)

- Corollary: reducing voltage requires reducing frequency

- 15% reduction in voltage requires about 15% slow down in frequency

- Increasing f requires V to be increased proportionally

- Intuitively: a higher frequency means a shorter cycle time, which means the critical path of your processor needs to be shorter, which requires faster transistors, which you get by increasing the voltage

- "Overclocking" just increases the clock speed without increasing voltage => machine might crash (cycle time shorter than the critical path delay)

- Corollary: reducing voltage requires reducing frequency

- 15% reduction in voltage requires about 15% slow down in frequency

- What's the impact on dynamic power? 0.85<sup>3</sup> ≈ 60% -> 40% dynamic power reduction.

## $P = k C f^3$

• Dynamic power favors parallel processing over higher clock rate

## $P = k C f^3$

- Dynamic power favors parallel processing over higher clock rate

- Take a core and replicate it 4 times: 4x speedup & 4x power

## $P = k C f^3$

- Dynamic power favors parallel processing over higher clock rate

- Take a core and replicate it 4 times: 4x speedup & 4x power

- Take a core and clock it 4 times faster: 4x speedup but 64x dynamic power!

# $\mathsf{P} = \mathsf{k} \mathsf{C} \mathsf{f}^3$

- Dynamic power favors parallel processing over higher clock rate

- Take a core and replicate it 4 times: 4x speedup & 4x power

- Take a core and clock it 4 times faster: 4x speedup but 64x dynamic power!

- Another way to think about this

# $\mathsf{P} = \mathsf{k} \mathsf{C} \mathsf{f}^3$

- Dynamic power favors parallel processing over higher clock rate

- Take a core and replicate it 4 times: 4x speedup & 4x power

- Take a core and clock it 4 times faster: 4x speedup but 64x dynamic power!

- Another way to think about this

- If a task can be perfectly parallelized by 4 cores, we can reduce the clock frequency of each core to 1/4 while retaining the same performance

# $\mathsf{P} = \mathsf{k} \mathsf{C} \mathsf{f}^3$

- Dynamic power favors parallel processing over higher clock rate

- Take a core and replicate it 4 times: 4x speedup & 4x power

- Take a core and clock it 4 times faster: 4x speedup but 64x dynamic power!

- Another way to think about this

- If a task can be perfectly parallelized by 4 cores, we can reduce the clock frequency of each core to 1/4 while retaining the same performance

- Dynamic power becomes  $4 \times (1/4)^3 = 1/16$

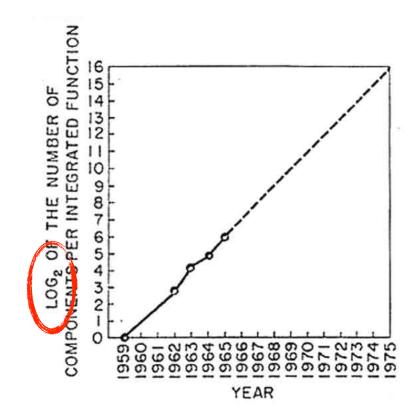

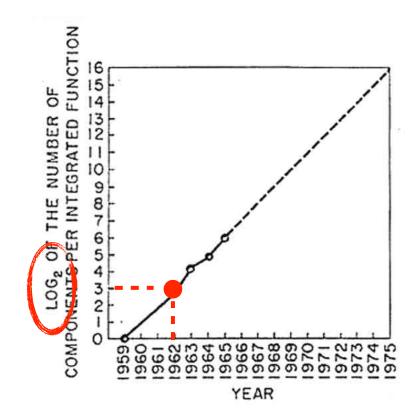

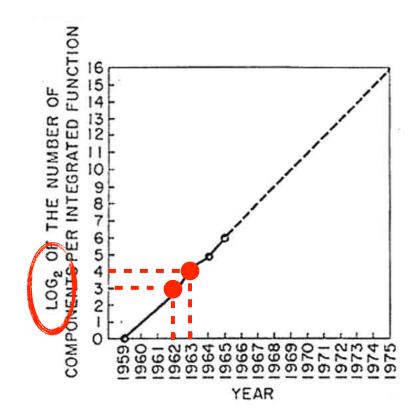

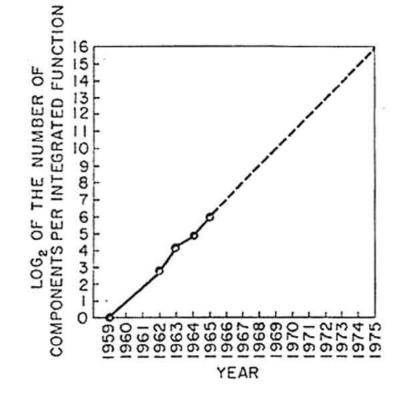

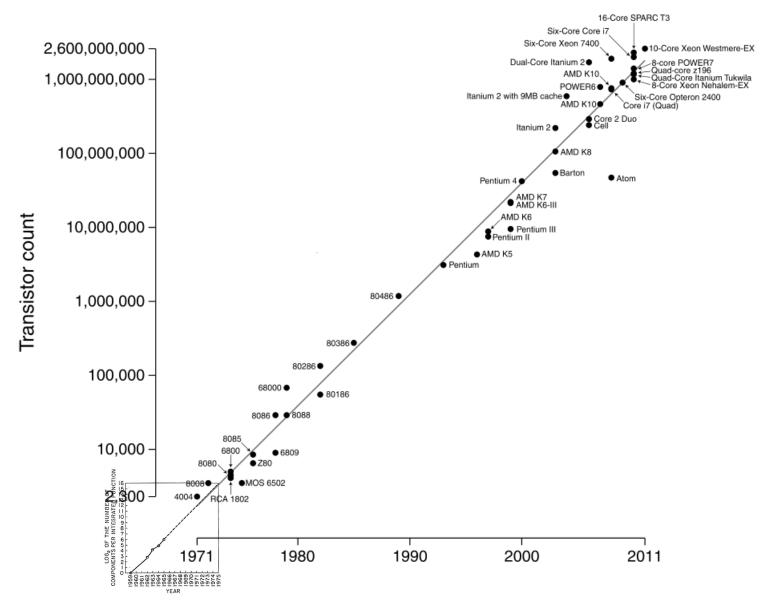

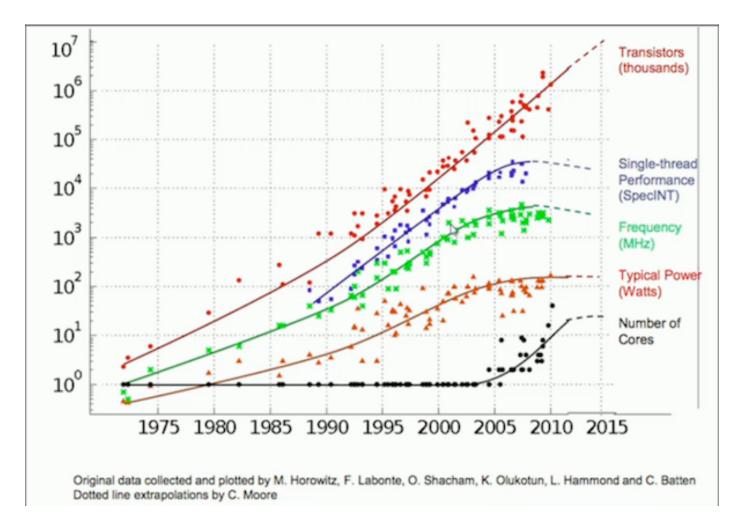

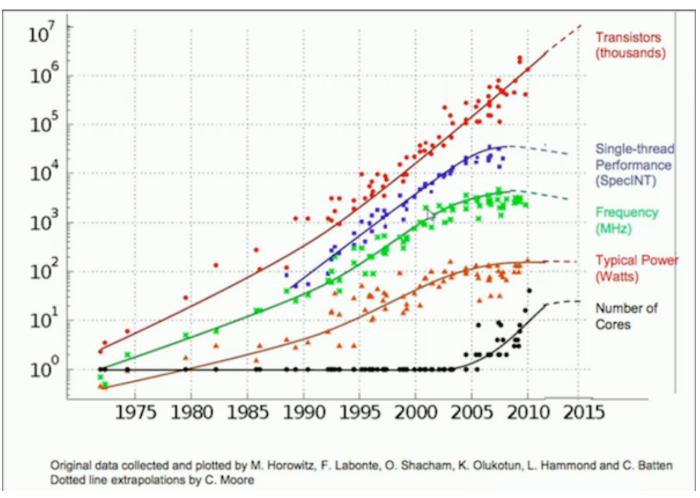

Gordon Moore in 1965 predicted that the number of transistors doubles every year

• Gordon Moore in 1965 predicted that the number of transistors doubles every year

• Gordon Moore in 1965 predicted that the number of transistors doubles every year

Gordon Moore in 1965 predicted that the number of transistors doubles every year

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- In 1975 he revised the prediction to doubling every 2 years

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- In 1975 he revised the prediction to doubling every 2 years

- Today's widely-known Moore's Law: number of transistors double about every 18 months (Moore never used the number 18...)

10

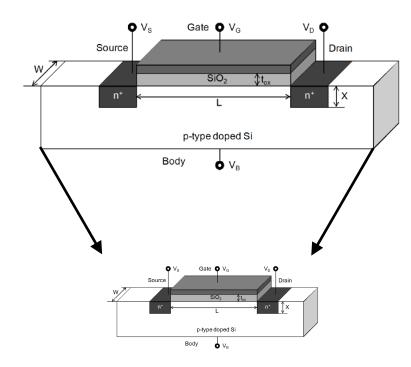

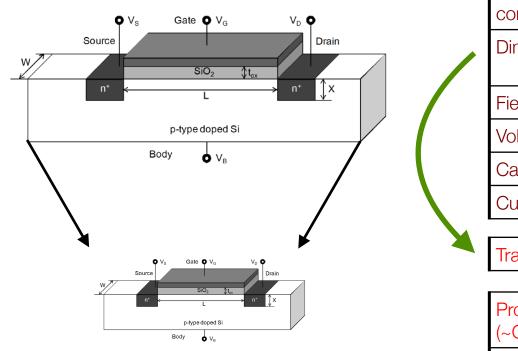

#### Scale factor $\alpha < 1$ $\alpha = 0.7 \Rightarrow 2X$ more transistors!

| Parameter                | Value        | Scaled<br>Value |

|--------------------------|--------------|-----------------|

| Dopant<br>concentrations | Na, Nd       | Na/a, Nd/<br>a  |

| Dimensions               | L, W,<br>Tox | aL, aW,<br>aTox |

| Field                    | E            | E               |

| Voltage                  | V            | αV              |

| Capacitance              | С            | aC              |

| Current                  |              | al              |

Scale factor  $\alpha < 1$  $\alpha = 0.7 \Rightarrow 2X$  more transistors!

| Parameter                | Value        | Scaled<br>Value  |  |  |  |

|--------------------------|--------------|------------------|--|--|--|

| Dopant<br>concentrations | Na, Nd       | Na/a, Nd/<br>a   |  |  |  |

| Dimensions               | L, W,<br>Tox | aL, aW,<br>aTox  |  |  |  |

| Field                    | E            | E                |  |  |  |

| Voltage                  | V            | αV               |  |  |  |

| Capacitance              | С            | aC               |  |  |  |

| Current                  |              | al               |  |  |  |

|                          | -            |                  |  |  |  |

| Transistors/Area         | d            | d/a <sup>2</sup> |  |  |  |

#### Scale factor $\alpha < 1$ $\alpha = 0.7 \Rightarrow 2X$ more transistors!

| Parameter                   | Value        | Scaled<br>Value  |     |

|-----------------------------|--------------|------------------|-----|

| Dopant<br>concentrations    | Na, Nd       | Na/a, Nd/<br>a   |     |

| Dimensions                  | L, W,<br>Tox | aL, aW,<br>aTox  |     |

| Field                       | E            | E                |     |

| Voltage                     | V            | αV               |     |

| Capacitance                 | С            | aC               |     |

| Current                     | I            | al               |     |

| Transistors/Area            | d            | d/a <sup>2</sup> | I ) |

| Propagation time<br>(~CV/I) | t            | at               |     |

| Frequency (1/t)             | f            | f/a              |     |

#### Scale factor $\alpha < 1$ $\alpha = 0.7 \Rightarrow 2X$ more transistors!

Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions. Proc. of IEEE. Dennart et al. 1974.

Scale factor  $\alpha < 1$  $\alpha = 0.7 \Rightarrow 2X$  more transistors!

| Parameter                     | Value        | Scaled<br>Value  |    |

|-------------------------------|--------------|------------------|----|

| Dopant<br>concentrations      | Na, Nd       | Na/a, Nd/<br>a   |    |

| Dimensions                    | L, W,<br>Tox | aL, aW,<br>aTox  |    |

| Field                         | E            | E                |    |

| Voltage                       | V            | αV               |    |

| Capacitance                   | С            | αC               |    |

| Current                       |              | al               |    |

| Transistors/Area              | d            | d/a <sup>2</sup> | Ι, |

| Propagation time<br>(~CV/I)   | t            | at               |    |

| Frequency (1/t)               | f            | f/a              |    |

|                               | ♦            |                  | -  |

| Power (CV <sup>2</sup> f)     | Р            | a <sup>2</sup> P |    |

| Power/area<br>(Power density) | Pd           | Pd               |    |

Design of Ion-Implanted MOSFET's with Very Small Physical Dimensions. Proc. of IEEE. Dennart et al. 1974.

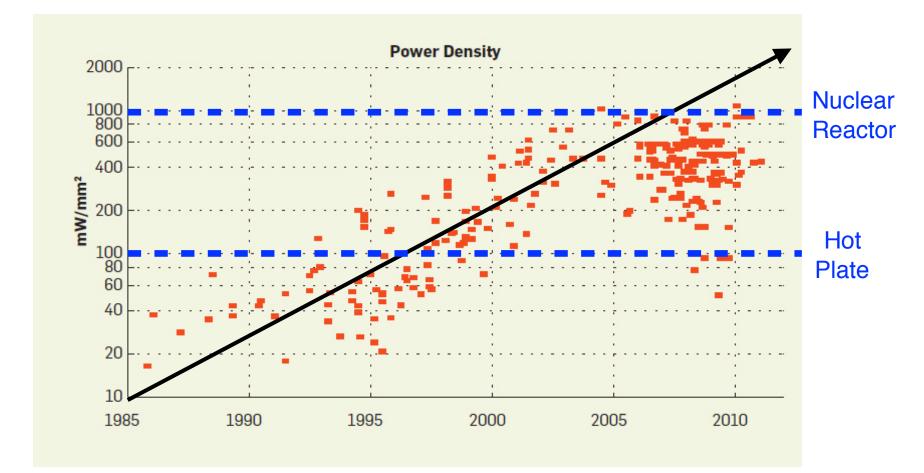

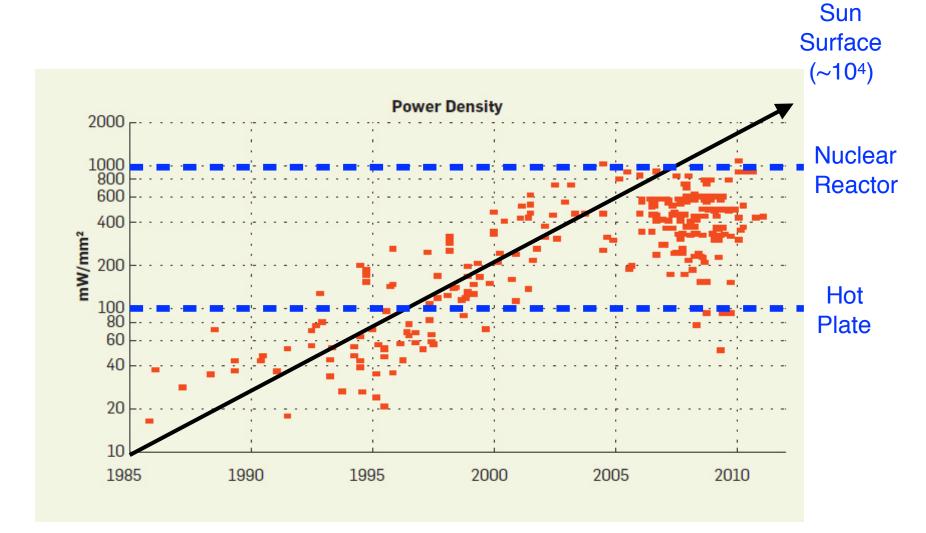

• Each new processor generation can have more transistors (Moore's Law), and will run at higher frequency but won't consume more power under the same area budget.

- Each new processor generation can have more transistors (Moore's Law), and will run at higher frequency but won't consume more power under the same area budget.

- More transistors means better microarchitecture, which leads to better performance even under the same frequency.

- Each new processor generation can have more transistors (Moore's Law), and will run at higher frequency but won't consume more power under the same area budget.

- More transistors means better microarchitecture, which leads to better performance even under the same frequency.

- Higher frequency means better performance even under the same microarchitecture.

- Each new processor generation can have more transistors (Moore's Law), and will run at higher frequency but won't consume more power under the same area budget.

- More transistors means better microarchitecture, which leads to better performance even under the same frequency.

- Higher frequency means better performance even under the same microarchitecture.

- Overall, software gets a free ride: wait for the next generation of hardware and performance will naturally increase without consuming more power.

#### Implications of Dennard Scaling and Moore's Law

- Each new processor generation can have more transistors (Moore's Law), and will run at higher frequency but won't consume more power under the same area budget.

- More transistors means better microarchitecture, which leads to better performance even under the same frequency.

- Higher frequency means better performance even under the same microarchitecture.

- Overall, software gets a free ride: wait for the next generation of hardware and performance will naturally increase without consuming more power.

Moore's law gave us more transistors; Dennard scaling made them useful. Bob Colwell, DAC 2013, June 4, 2013

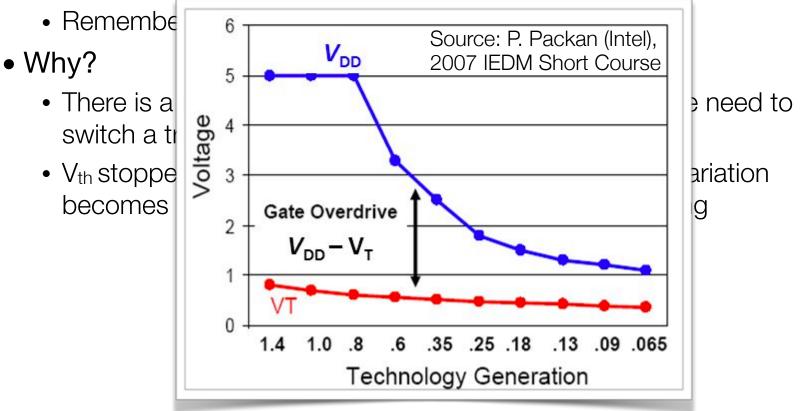

- What Happened?

- Supply voltage  $V_{dd}$  stops scaling (Can't drop voltage below ~1 V)

- Remember Power =  $CV^{2}f$

- What Happened?

- Supply voltage V<sub>dd</sub> stops scaling (Can't drop voltage below ~1 V)

- Remember Power =  $CV^{2}f$

- Why?

- There is a fundamental limit as to how much voltage we need to switch a transistor, called threshold voltage (V<sub>th</sub>).

- V<sub>th</sub> stopped scaling because leakage power/reliability/variation becomes huge issues, and accordingly V<sub>dd</sub> stops scaling

#### • What Happened?

• Supply voltage  $V_{dd}$  stops scaling (Can't drop voltage below ~1 V)

- What Happened?

- Supply voltage  $V_{dd}$  stops scaling (Can't drop voltage below ~1 V)

- Remember Power =  $CV^{2}f$

- Why?

- There is a fundamental limit as to how much voltage we need to switch a transistor, called threshold voltage ( $V_{th}$ ).

- V<sub>th</sub> stopped scaling because leakage power/reliability/variation becomes huge issues, and accordingly V<sub>dd</sub> stops scaling

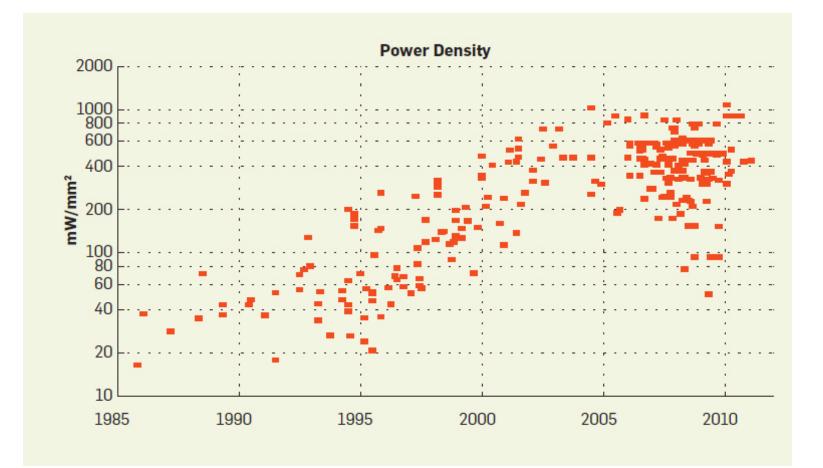

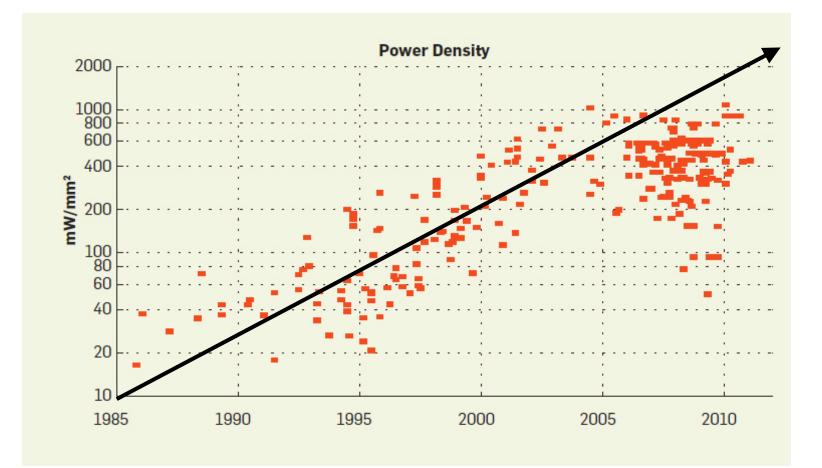

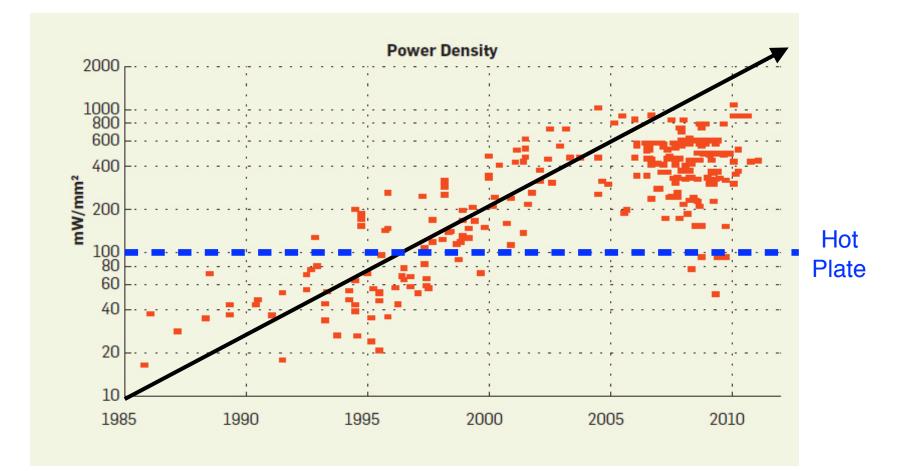

- The demise of Dennard Scaling means the power density (power consumption per unit area) will increase rather than staying stable.

#### **Dark Silicon**

n. [därk, sĭl'ĭ-kən, -kŏn']

More transistors on chip (due to Moore's Law), but a growing fraction cannot actually be used due to power limits (due to the end of Dennard Scaling).

• Initial response has been to lower frequency and increase cores / chip

• Initial response has been to lower frequency and increase cores / chip

- Initial response has been to lower frequency and increase cores / chip

- There is a limit to core scaling. Why?

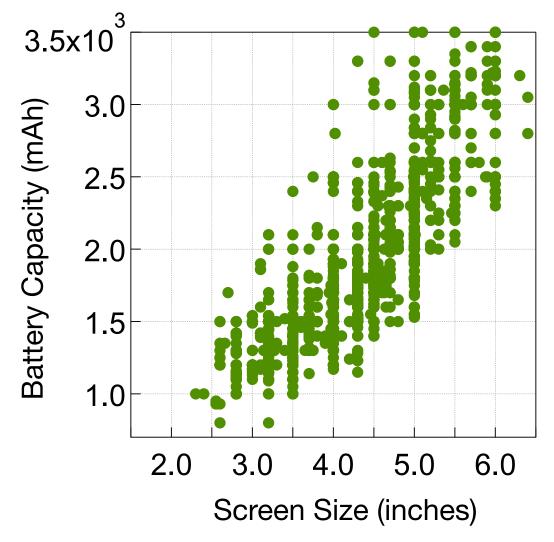

#### 2007: A Revolutionary New Computer

**OPINION**

# No Moore's Law for batteries

#### Fred Schlachter<sup>1</sup>

American Physical Society, Washington, DC 20045

The public has become accustomed to rapid progress in mobile phone technology, computers, and access to information; tablet computers, smart phones, and other powerful new devices are familiar to most people on the planet.

These developments are due in part to the ongoing exponential increase in computer processing power, doubling approximately every 2 years for the past several decades. This pattern is usually called Moore's Law and is named for Gordon Moore, a cofounder of Intel. The law is not a law like that for gravity; it is an empirical observation, which has become a self-fulfilling prophecy. Unfortunately, much of the public has come to expect that all technology does, will, or should follow such a law, which is not consistent with our everyday observations: For example, the maximum there is a Moore's Law for computer processors is that electrons are small and they do not take up space on a chip. Chip performance is limited by the lithography technology used to fabricate the chips; as lithography improves ever smaller features can be made on processors. Batteries are not like this. Ions, which transfer charge in batteries, are large, and they take up space, as do anodes, cathodes, and electrolytes. A D-cell battery stores more energy than an AA-cell. Potentials in a battery are dictated by the relevant chemical reactions, thus limiting eventual battery performance. Significant improvement in battery capacity can only be made by changing to a different chemistry.

Scientists and battery experts, who have been optimistic in the recent past about improving lithium-ion batteries and about de-

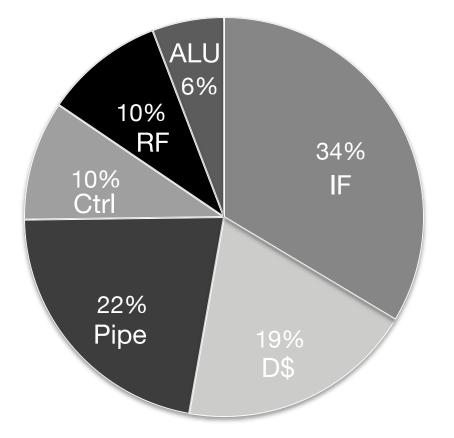

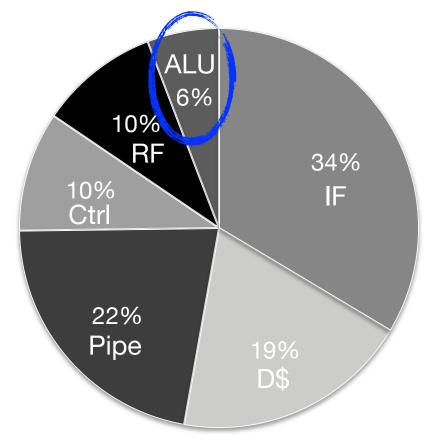

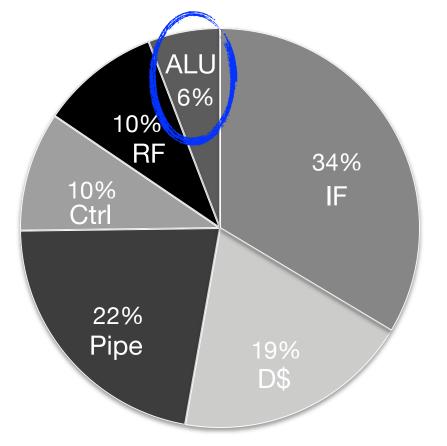

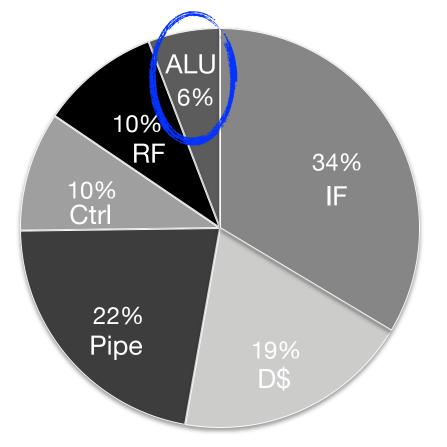

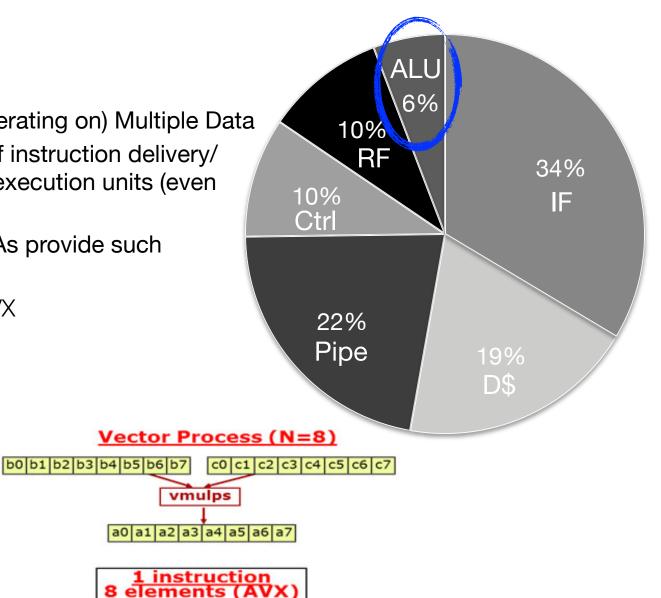

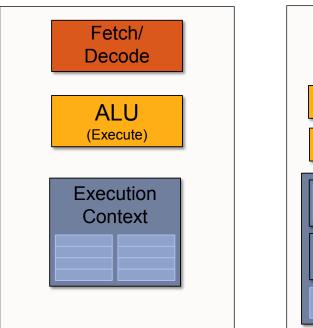

General-Purpose CPU = Instruction Delivery + Data Feeding + Execution + Control, where instruction delivery, data feeding & control are pure overhead

General-Purpose CPU = Instruction Delivery + Data Feeding + Execution + Control, where instruction delivery, data feeding & control are pure overhead

IF: Instruction fetch

Ctrl: Other control logics

Pipe: Pipeline reg, bus, clock

D\$: Data cache

RF: Register file

ALU: Functional units

General-Purpose CPU = Instruction Delivery + Data Feeding + Execution + Control, where instruction delivery, data feeding & control are pure overhead

IF: Instruction fetch

Ctrl: Other control logics

Pipe: Pipeline reg, bus, clock

D\$: Data cache

RF: Register file

ALU: Functional units

General-Purpose CPU = Instruction Delivery + Data Feeding + Execution + Control, where instruction delivery, data feeding & control are pure overhead

#### **Pure Overhead**

IF: Instruction fetch

Ctrl: Other control logics

Pipe: Pipeline reg, bus, clock

D\$: Data cache

RF: Register file

ALU: Functional units

General-Purpose CPU = Instruction Delivery + Data Feeding + Execution + Control, where instruction delivery, data feeding & control are pure overhead

#### **Pure Overhead**

IF: Instruction fetch

Ctrl: Other control logics

Pipe: Pipeline reg, bus, clock

D\$: Data cache

RF: Register file

ALU: Functional units

Doing Actual Work

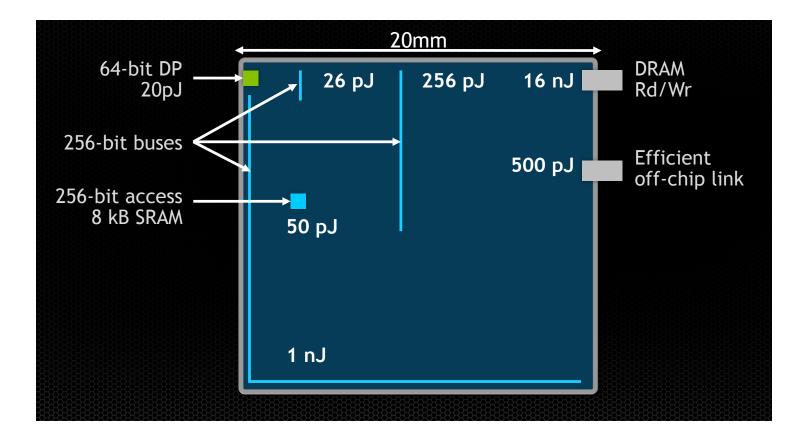

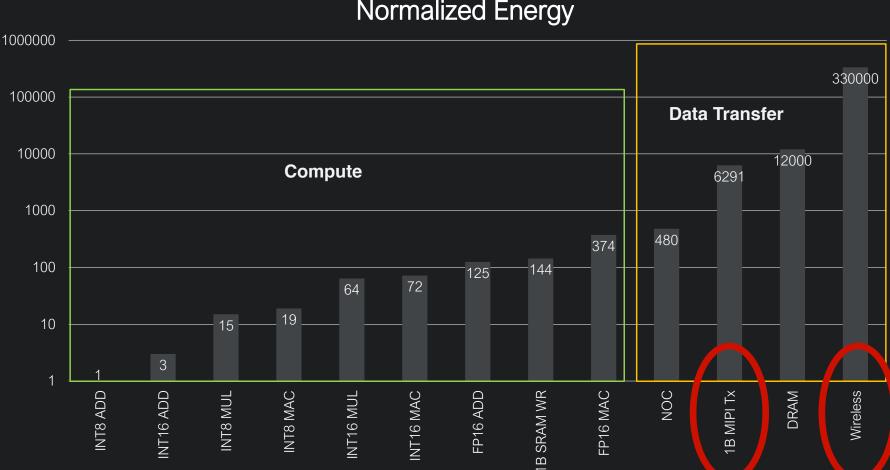

### **Computation vs. Data Movement**

Data movement energy >> computation energy

Challenges for future computing systems, Bill Dally, 2015

#### **Computation vs. Data Movement**

Data movement energy >> computation energy

Normalized Energy

# SIMD

- Single Instruction (operating on) Multiple Data

- Amortizing the cost of instruction delivery/ control across many execution units (even cores).

- Almost all modern ISAs provide such instructions:

- x86: MMX/SSE/AVX

c0 c1 c2 c3

a3

Arm: Neon

Scalar Process

XXX

a1 a2

4 instructions 4 elements

b0 b1 b2 b3

a0

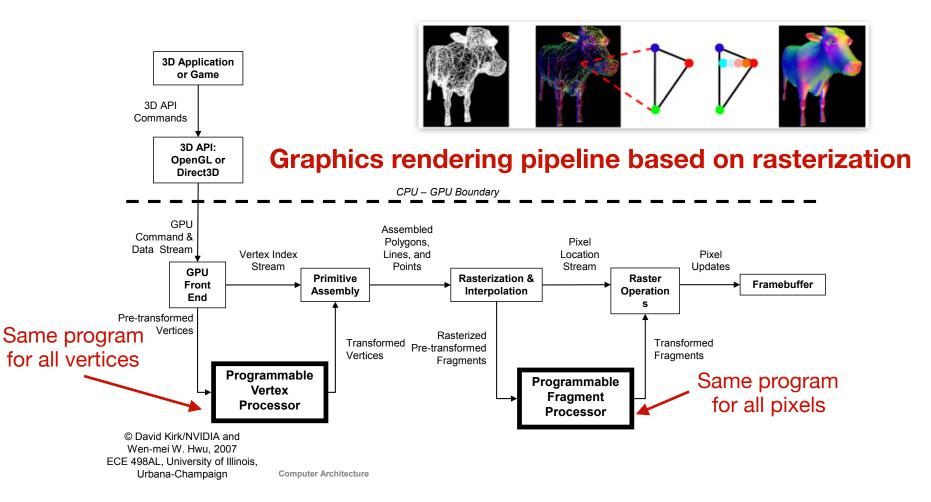

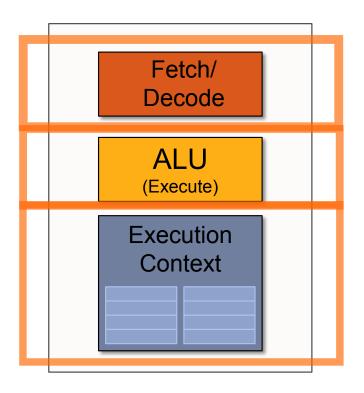

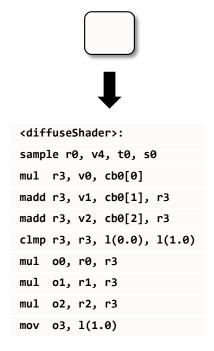

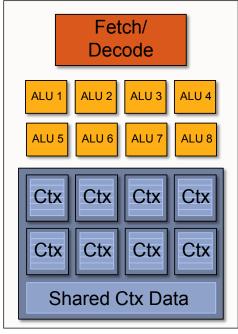

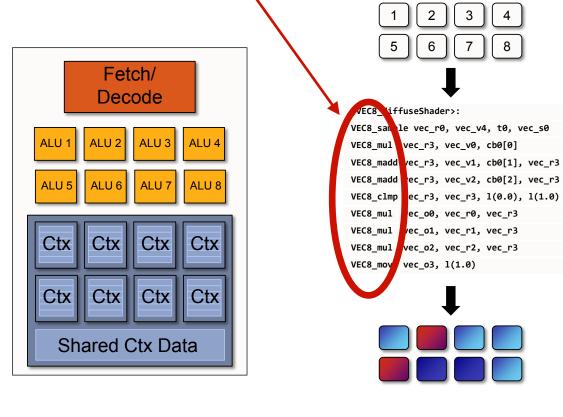

# Graphics Processing Units/GPUs (SIMT)

• Designed for graphics rendering, which is massively parallel.

#### **Execute shader**

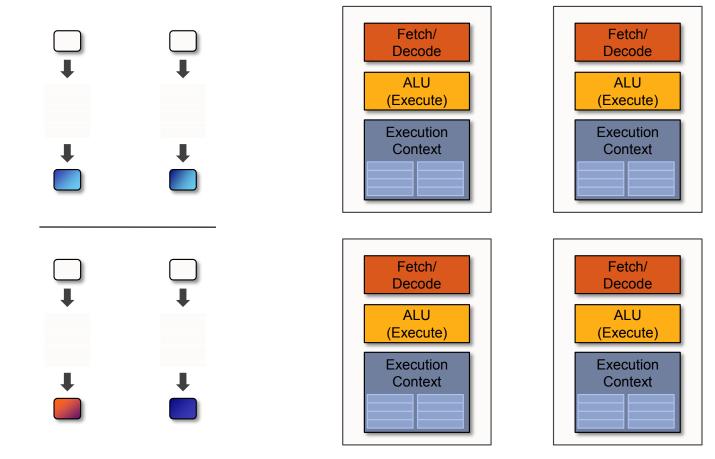

#### **Two cores** (two fragments in parallel)

#### fragment 1 fragment 2 Fetch/ Fetch/ Decode Decode <diffuseShader>: <diffuseShader>: sample r0, v4, t0, s0 **ALU** ALU sample r0, v4, t0, s0 mul r3, v0, cb0[0] mul r3, v0, cb0[0] madd r3, v1, cb0[1], r3 madd r3, v1, cb0[1], r3 (Execute) (Execute) madd r3, v2, cb0[2], r3 madd r3, v2, cb0[2], r3 clmp r3, r3, l(0.0), l(1.0) clmp r3, r3, l(0.0), l(1.0) mul 00, r0, r3 mul 00, r0, r3 mul 01, r1, r3 Execution Execution mul 01, r1, r3 mul o2, r2, r3 mul o2, r2, r3 mov o3, l(1.0) Context Context mov o3, 1(1.0)

23

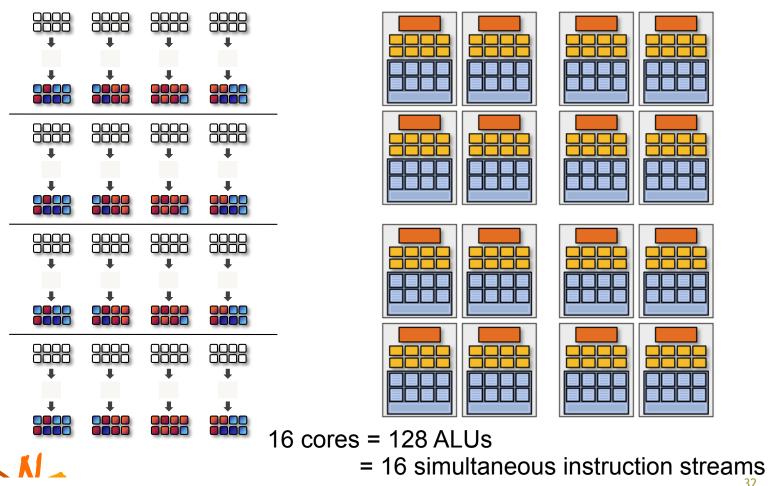

#### Four cores (four fragments in parallel)

24

#### Sixteen cores (sixteen fragments in parallel)

25

#### Instruction stream coherence

But... many fragments should be able to share an instruction stream!

| <diffuseshader>:</diffuseshader> |     |     |       |    |        |

|----------------------------------|-----|-----|-------|----|--------|

| sample r0, v4, t0, s0            |     |     |       |    |        |

| mul                              | r3, | v0, | cb0[0 | ]  |        |

| madd                             | r3, | v1, | cb0[1 | ], | r3     |

| madd                             | r3, | v2, | cb0[2 | ], | r3     |

| clmp                             | r3, | r3, | 1(0.0 | ), | 1(1.0) |

| mul                              | 00, | r0, | r3    |    |        |

| mul                              | 01, | r1, | r3    |    |        |

| mul                              | 02, | r2, | r3    |    |        |

| mov                              | ο3, | 1(1 | .0)   |    |        |

Amortize cost/complexity of managing an instruction stream across many ALUs

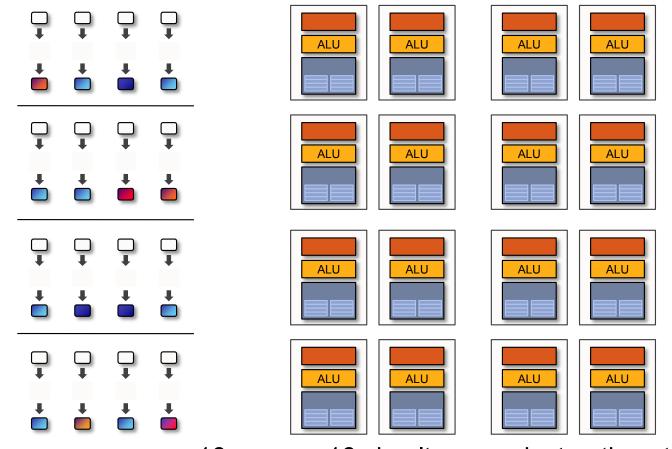

#### SIMD processing

Kayvon Fatahalia

Kayvon Fatahalian, 2008

28

SIMD/vector instructions, each operates on a vector of 8 elements here.

Kayvon Fatahalian, 2008

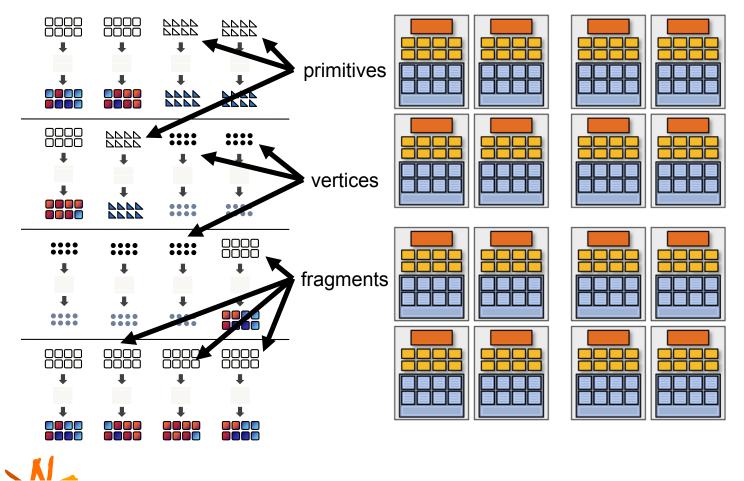

#### 16 cores, each with 8 ALUs. Each core here runs the same program (fragment shader)

Kayvon Fatahaliane382N: Principles of Computer Architecture

Kayvon Fatahalian, 2008

32

#### 16 cores, each with 8 ALUs. Cores here run different programs

(some are processing vertices, some are processing fragments)

34

33

#### Each Core Does Fine-Grained Multi-threading

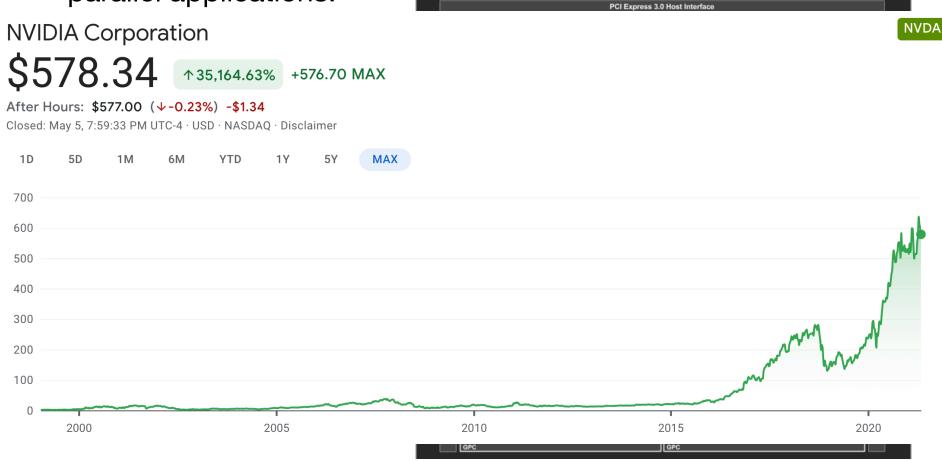

# Nvidia Maxwell GPU (2014)

- Today: General Purpose GPU (GPGPU), used for any massive parallel applications:

- Physics simulation

- Deep learning

- Computer vision

# Nvidia Maxwell GPU (2014)

• Today: General Purpose GPU (GPGPU), used for any massive parallel applications:

• GPUs are very efficient for massively parallel program

- GPUs are very efficient for massively parallel program

- But are still fairly general, so there are still many inefficiencies

- Still need to fetch and decode instructions

- Still have (very large) caches, so data delivery isn't efficient

- GPUs are very efficient for massively parallel program

- But are still fairly general, so there are still many inefficiencies

- Still need to fetch and decode instructions

- Still have (very large) caches, so data delivery isn't efficient

- Idea: instead of building general-purpose processors that can do everything, but inefficiently, let's build specialized processors that can only do limited things, but extremely efficiently.

- GPUs are very efficient for massively parallel program

- But are still fairly general, so there are still many inefficiencies

- Still need to fetch and decode instructions

- Still have (very large) caches, so data delivery isn't efficient

- Idea: instead of building general-purpose processors that can do everything, but inefficiently, let's build specialized processors that can only do limited things, but extremely efficiently.

- A.k.a., domain-specific accelerators

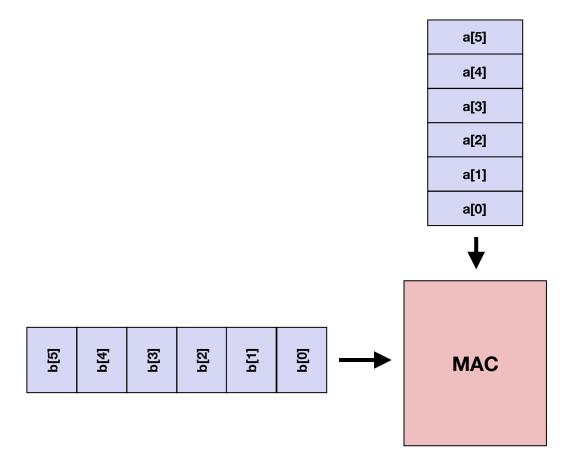

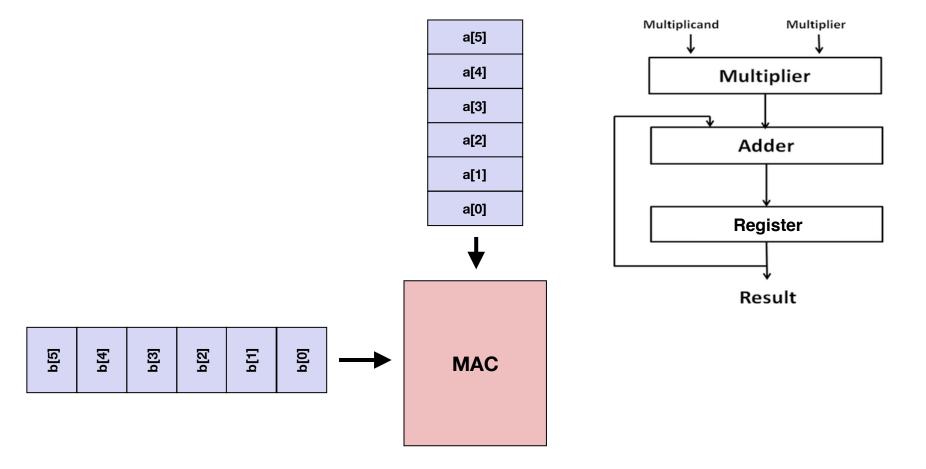

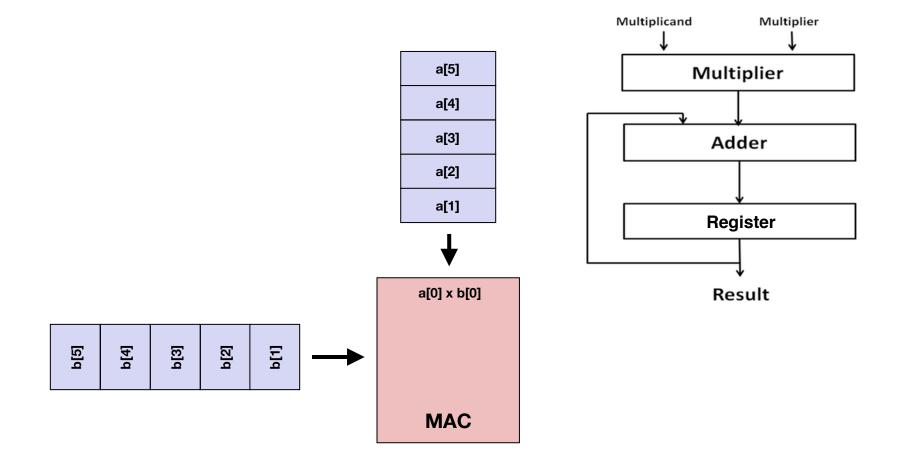

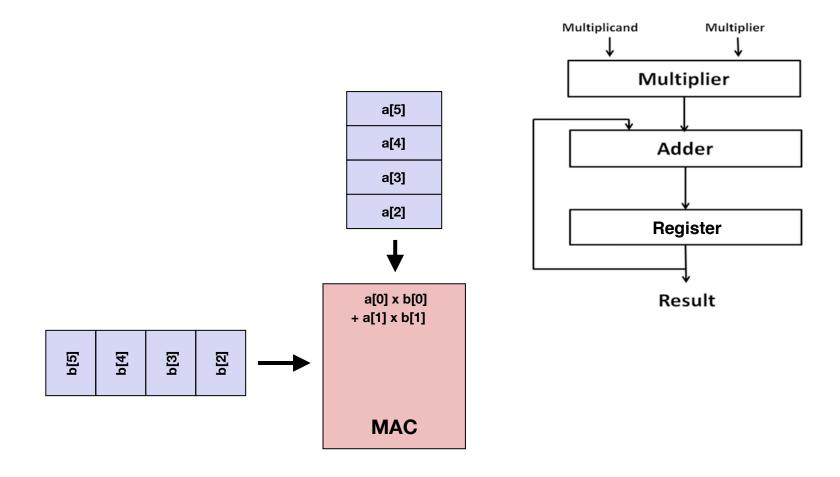

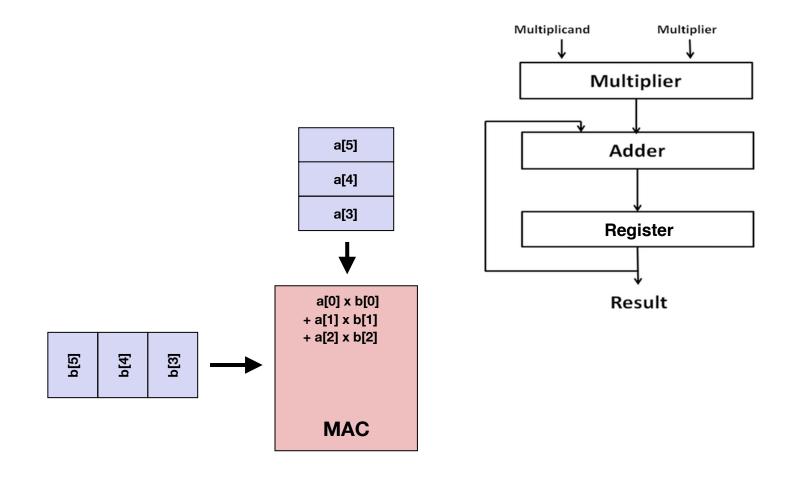

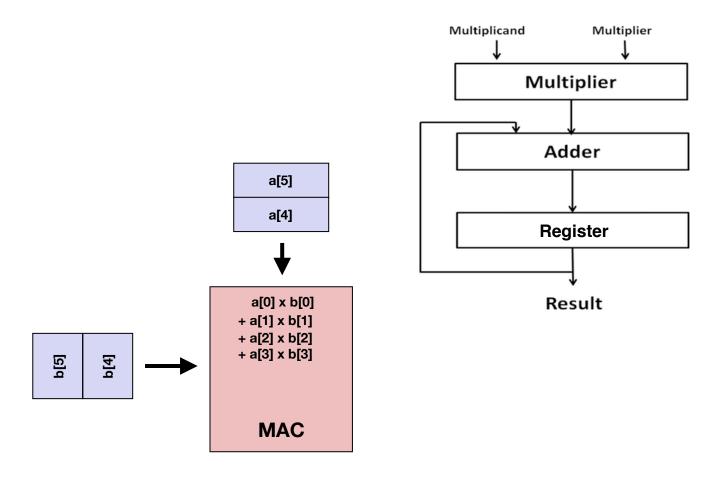

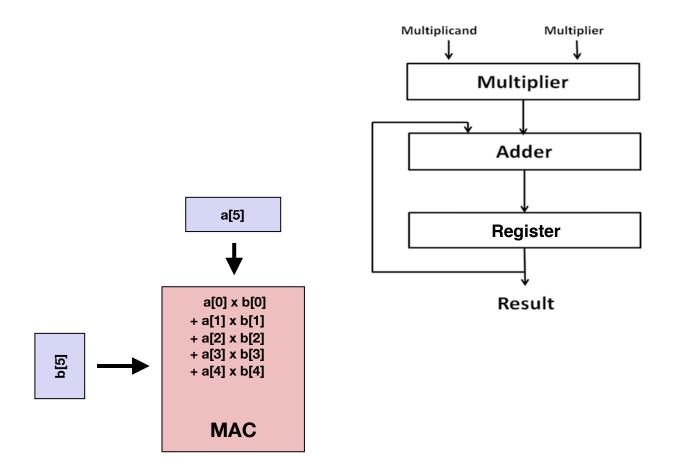

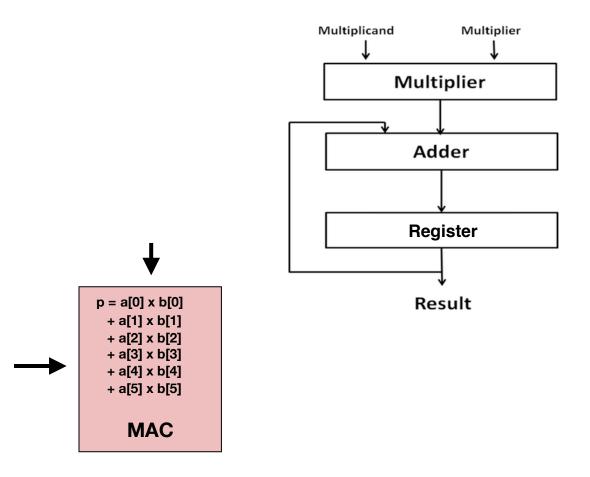

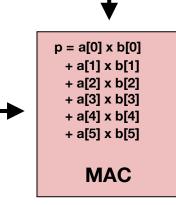

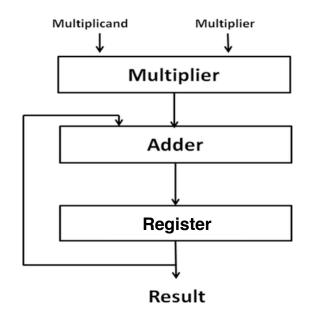

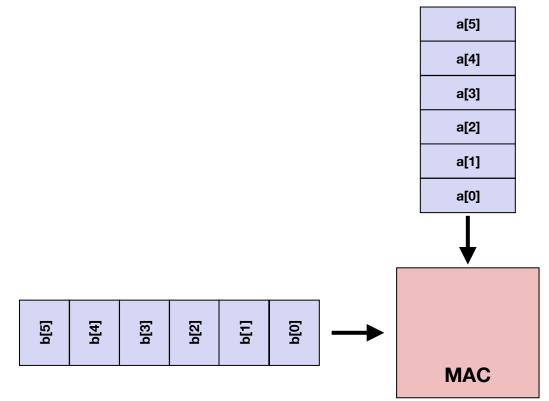

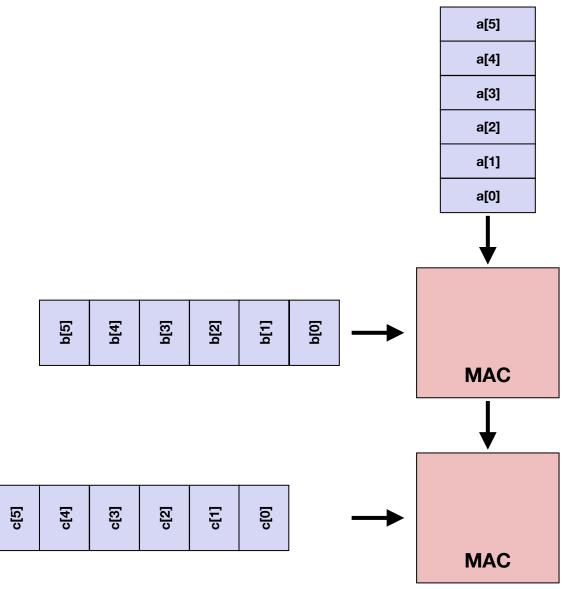

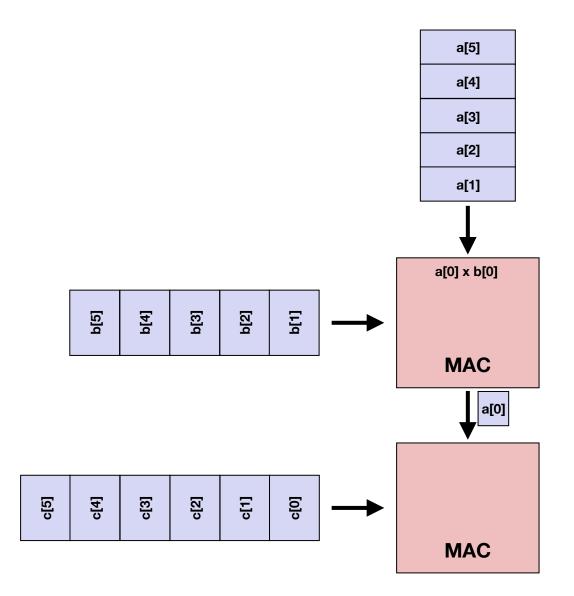

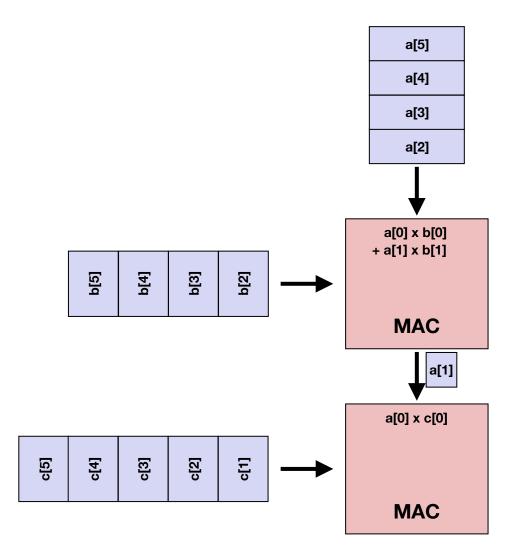

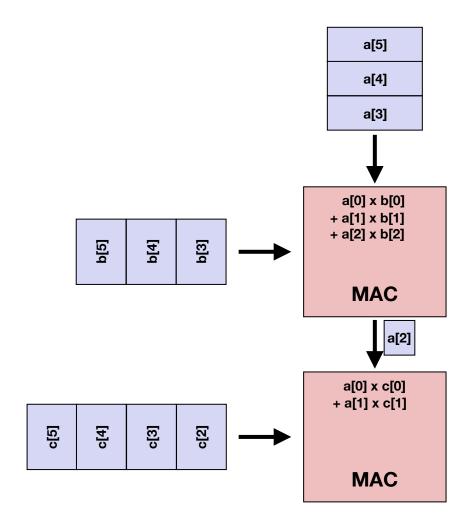

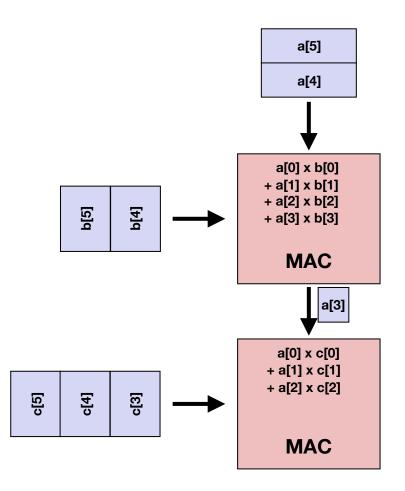

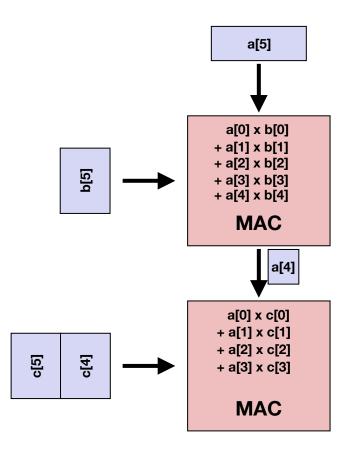

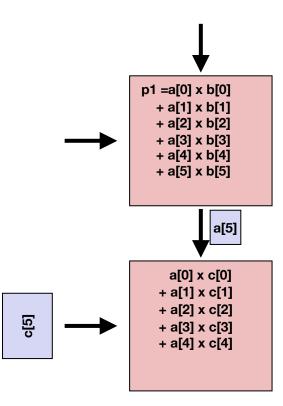

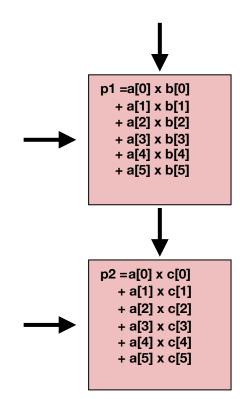

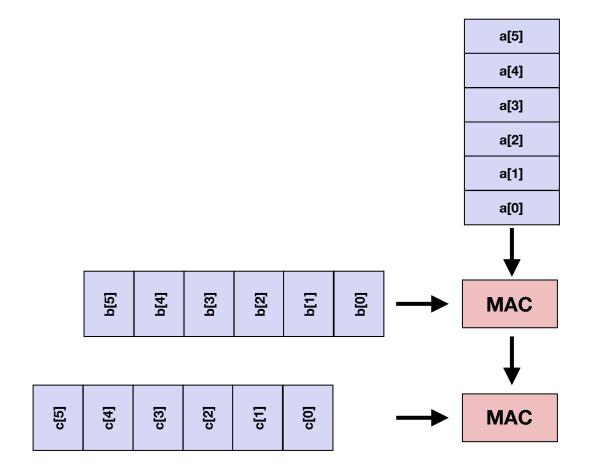

- Does nothing but vector dot product

- No instruction fetch and decode (there is no instruction)

- The register is close to the ALU and gets reused over and over: good data delivery efficiency

- Very simple control

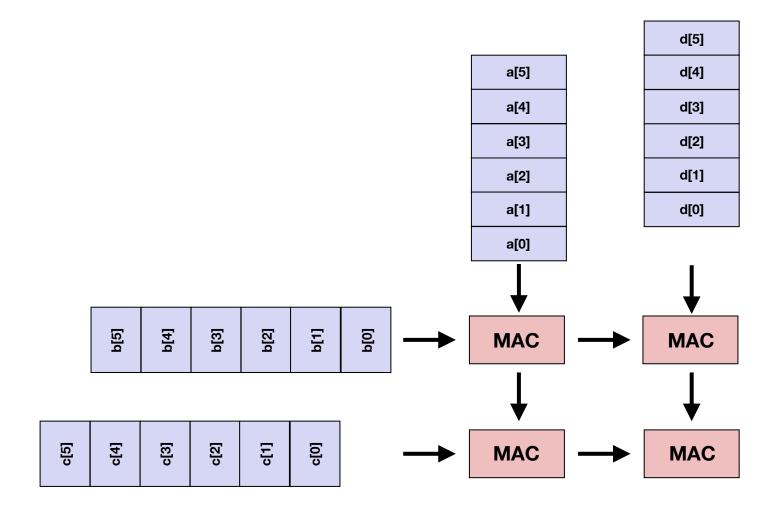

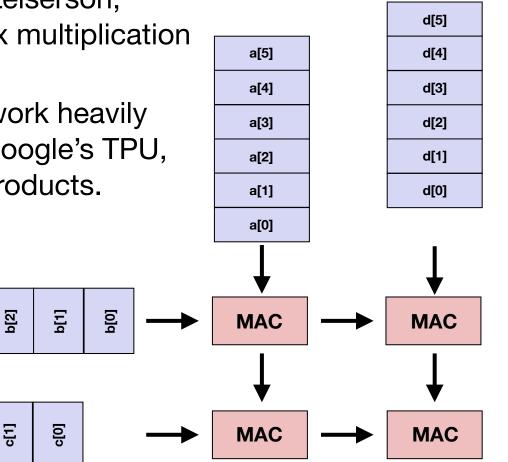

#### **Matrix Matrix Multiplication**

#### **Matrix Matrix Multiplication**

# **Matrix Matrix Multiplication**

- Systolic array (Kung & Leiserson, 1978). Basically a matrix multiplication engine.

- Convolution neural network heavily relies on this. Used in Google's TPU, among other industry products.

b[4]

c[3]

b[5]

c[4]

c[5]

b[3]

c[2]

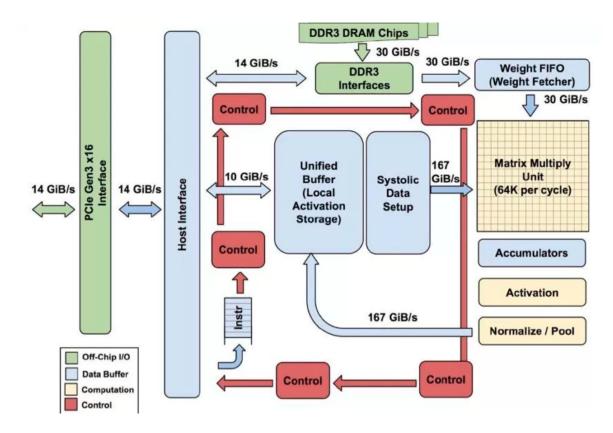

# **Google Tensor Processing Unit**

- Convolution in deep learning can be transformed to matrix multiplication.

- TPU: specialized processor (i.e., systolic array architecture) for tensor processing (matrix multiply)

- 30x~80x more power-efficient than GPU

## **Another Domain: Video Compression**

# **Another Domain: Video Compression**

30-second video @ 1080p resolution (1920 x 1080 pixels per frame) @ 30 frames per second (FPS) 3 colors per pixel + 1 byte per color  $\rightarrow$  6.2 MB/frame  $\rightarrow$  6.2 MB x 30 s x 30 FPS = 5.2 GB total size Actual H.264 video file size: 65.4 MB (**80-to-1 compression ratio**). **Compression/encoding done in real-time without you even realizing it!**

#### **Another Domain: Computational Photography**

- Use computational algorithms to mimic a DSLR.

- Must be done in real-time. Executed on a dedicated Image Signal Processor (ISP).

**Conventional cameras**

Today's "cameras"

## Another Domain: Computational Photography

Portrait mode: simulate a large aperture

HDR mode: simulate a high dynamic range sensor

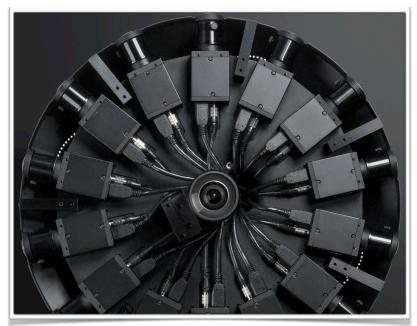

# 360° (VR/Panoramic) Videos and Photos

# **VR Video Capturing**

#### **Facebook Surround 360**

#### **Google Jump VR**

https://static.googleusercontent.com/media/research.google.com/en//pubs/archive/45617.pdf https://www.wired.com/2016/04/heres-360-degree-video-camera-facebook-giving-away/ https://twitter.com/yitechnology/status/918116570559336448

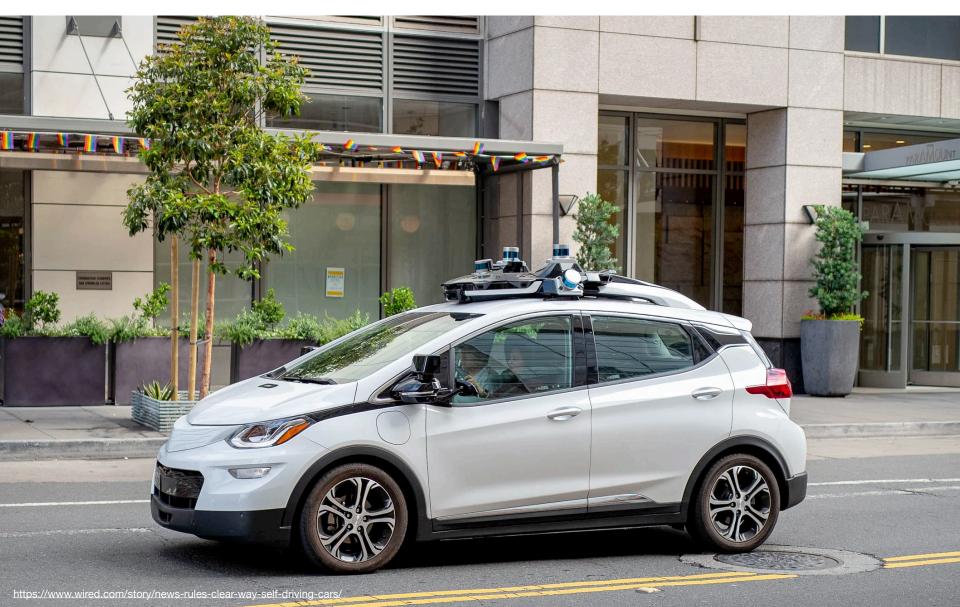

# **Autonomous Machines**

#### **Autonomous Machines**

## **Photorealistic Rendering**

## **Photorealistic Rendering**

# **Photorealistic Rendering**

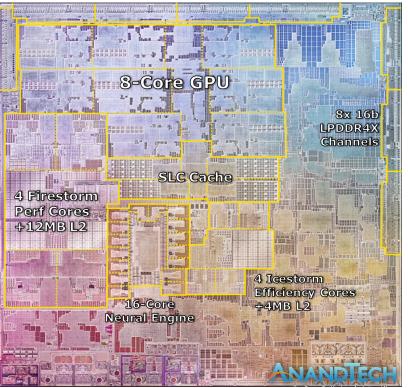

#### **Today's Processor Chips are Full of Accelerators**

https://www.techradar.com/news/apple-m1-chip https://www.anandtech.com/show/16226/apple-silicon-m1-a14-deep-dive

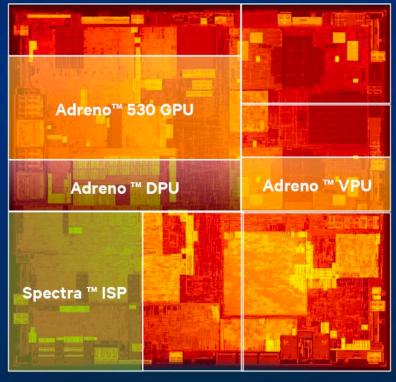

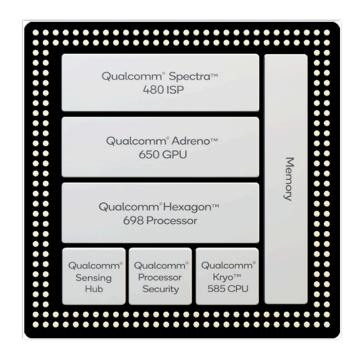

#### **Today's Processor Chips are Full of Accelerators**

Qualcomm Snapdragon 820 SoC

<sup>\*</sup> Not to scale

Qualcomm Snapdragon 835 SoC

# **Traditional Scope of Computer Systems**

• Take a program and try to figure out how to best execute on the hardware

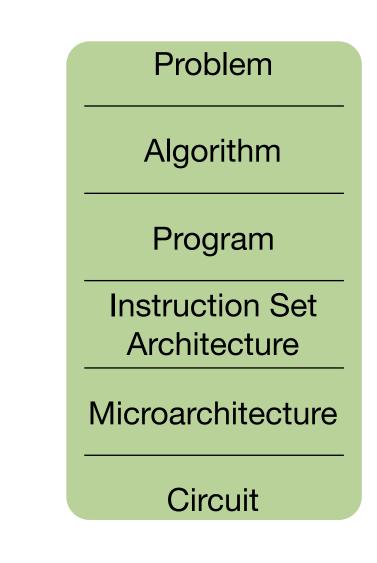

# **Real Scope of Computer Systems**

- Understand the problem to be solved, design algorithms, understand algorithms characteristics to design the best computer systems.

- It's no longer enough to work with a given program without understanding it.

# CSC 292/572: Mobile Visual Computing

Computational photography

Display and lightning systems

**Computer graphics**

#### AR/VR

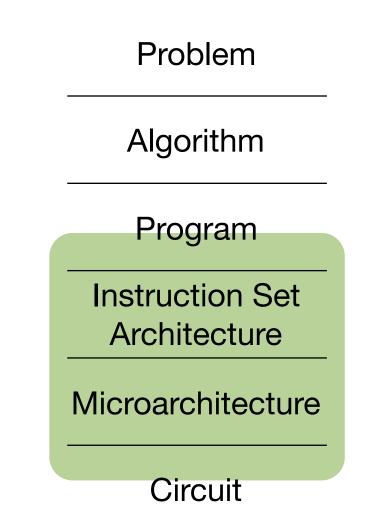

Video/image compression Problem

Algorithm

Program

Instruction Set Architecture

Microarchitecture

Circuit

# The Most Important Take Away of 252

- "There is no magic."

- Every thing can be derived from first principles. Trust your logical reasoning.

- Apply to virtually everything in science and engineering.

#### The Second Most Important Take Away of 252

- "Things don't have to be this way."

- As long as you don't violate physics, you can design a computer however you want.

- But every design decision you make usually involves certain tradeoffs. Be clear what your design goal is.

# The Third Most Important Take Away of 252

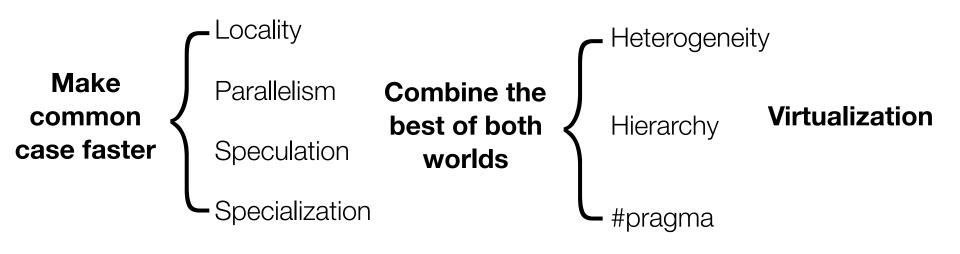

- Virtual all computer system design practices follow a small set of basic principles.

- It is these basic principles that are important, not the practices.