# CSC 252: Computer Organization Spring 2023: Lecture 6

#### Instructor: Yuhao Zhu

Department of Computer Science University of Rochester

#### Announcement

- Programming Assignment 1 is due tonight

- Details: <u>https://www.cs.rochester.edu/courses/252/</u> <u>spring2023/labs/assignment1.html</u>

- You have 3 slip days

#### Announcement

• Programming assignment 2 is out. It's in x86 assembly language. Details at: <u>https://www.cs.rochester.edu/</u> <u>courses/252/spring2023/labs/assignment2.html</u>.

| 22 | 23  | 24 | 25    | 26 | ø<br>Today | 28 |

|----|-----|----|-------|----|------------|----|

| 29 | 30  | 31 | Feb 1 | 2  | 3          | 4  |

| 5  | 6   | 7  | 8     | 9  | 10         | 11 |

| 12 | Due | 14 | 15    | 16 | 17         | 18 |

# Announcement

- You might still have three slip days.

- Read the instructions before getting started!!!

- You get 1/4 point off for every wrong answer

- Maxed out at 10

- TAs are best positioned to answer your questions about programming assignments!!!

- Programming assignments do NOT repeat the lecture materials. They ask you to synthesize what you have learned from the lectures and work out something new.

- Logics and arithmetics problem set: <u>https://</u> <u>www.cs.rochester.edu/courses/252/spring2023/</u> <u>handouts.html</u>.

- Not to be turned in.

# Intel x86 ISA Evolution (Milestones)

• Evolutionary design: Added more features as time goes on

# Intel x86 ISA Evolution (Milestones)

• Evolutionary design: Added more features as time goes on

| Date | Feature                                            | Notable<br>Implementation |

|------|----------------------------------------------------|---------------------------|

| 1974 | 8-bit ISA                                          | 8080                      |

| 1978 | 16-bit ISA (Basis for IBM PC & DOS)                | 8086                      |

| 1980 | Add Floating Point instructions                    | 8087                      |

| 1985 | 32-bit ISA (Refer to as IA32)                      | 386                       |

| 1997 | Add Multi-Media eXtension (MMX)                    | Pentium/MMX               |

| 1999 | Add Streaming SIMD Extension (SSE)                 | Pentium III               |

| 2001 | Intel's first attempt at 64-bit ISA (IA64, failed) | Itanium                   |

| 2004 | Implement AMD's 64-bit ISA (x86-64, AMD64)         | Pentium 4E                |

| 2008 | Add Advanced Vector Extension (AVE)                | Core i7 Sandy Bridge      |

# Our Coverage

- IA32

- The traditional x86

- 2<sup>nd</sup> edition of the textbook

- x86-64

- The standard

- CSUG machine

- 3<sup>rd</sup> edition of the textbook

- Our focus

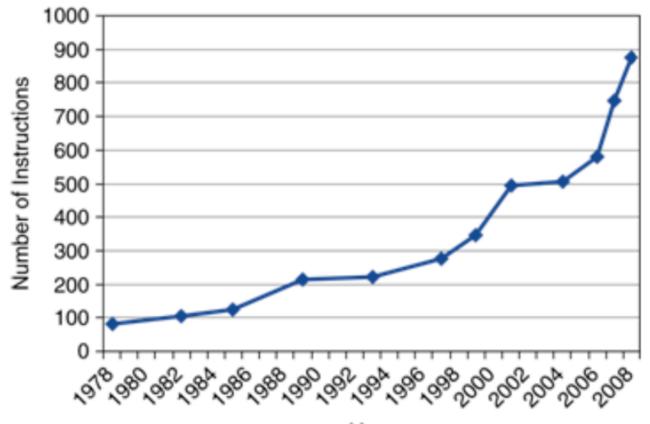

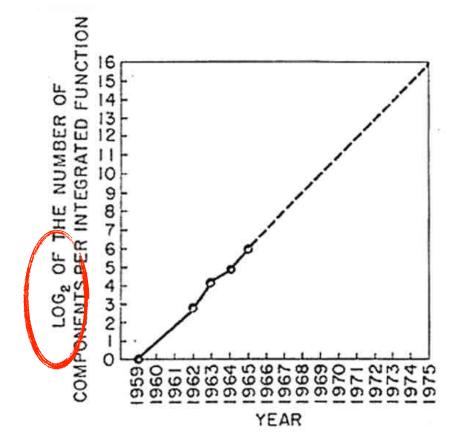

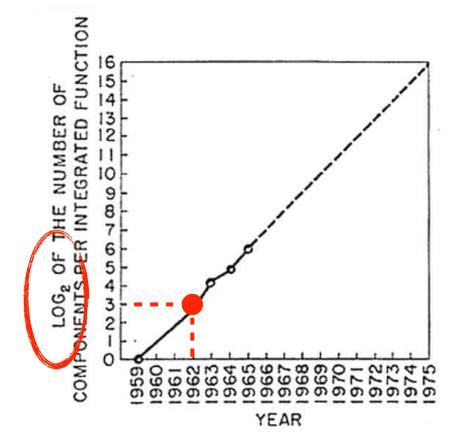

• More instructions typically require more transistors to implement

• More instructions typically require more transistors to implement

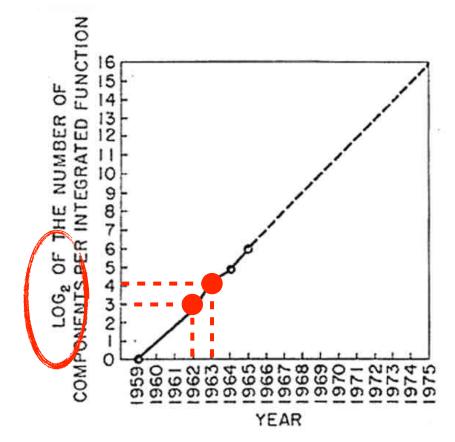

Year

More instructions typically require more transistors to implement

• More instructions require more transistors to implement

- More instructions require more transistors to implement

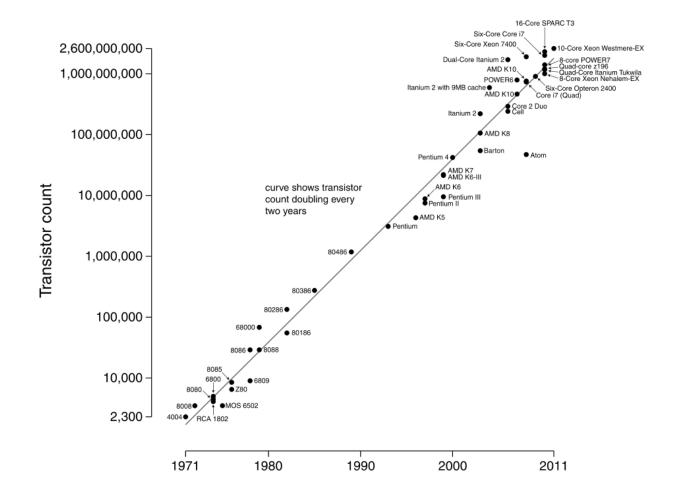

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- More instructions require more transistors to implement

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- More instructions require more transistors to implement

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- More instructions require more transistors to implement

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- More instructions require more transistors to implement

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- In 1975 he revised the prediction to doubling every 2 years

- More instructions require more transistors to implement

- Gordon Moore in 1965 predicted that the number of transistors doubles every year

- In 1975 he revised the prediction to doubling every 2 years

- Today's widely-known Moore's Law: number of transistors double about every 18 months

- Moore never used the number 18...

• Question: why is transistor count increasing but computers are becoming smaller?

- Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

• Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

• Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

- A law of math?

• Question: why is transistor count increasing but computers are becoming smaller?

No

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

- A law of math?

• Question: why is transistor count increasing but computers are becoming smaller?

No

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

- A law of math?

- A law of economy?

• Question: why is transistor count increasing but computers are becoming smaller?

Yes

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

No

- A law of math?

No

- A law of economy?

ars **TECHNICA**

BIZ & IT TECH SCIENCE POLICY CARS GAMING & CULTURE

#### TECH-

#### Transistors will stop shrinking in 2021, but Moore's law will live on

Final semiconductor industry roadmap says the future is 3D packaging and cooling.

The first problem has been known about for a long while. Basically, starting at around the 65nm node in 2006, the economic gains from moving to smaller transistors have been slowly dribbling away. Previously, moving to a smaller node meant you could cram tons more chips onto a single silicon wafer, at a reasonably small price increase. With recent nodes like 22 or 14nm, though, there are so many additional steps required that it costs a lot more to manufacture a completed wafer—not to mention additional costs for things like package-on-package (PoP) and through-silicon vias (TSV) packaging.

ars **TECHNICA**

BIZ & IT TECH SCIENCE POLICY CARS GAMING & CULTURE

#### TECH-

#### Transistors will stop shrinking in 2021, but Moore's law will live on

Final semiconductor industry roadmap says the future is 3D packaging and cooling.

The first problem has been known about for a long while. Basically, starting at around the 65nm node in 2006, the economic gains from moving to smaller transistors have been slowly dribbling away. Previously, moving to a smaller node meant you could cram tons more chips onto a single silicon wafer, at a reasonably small price increase. With recent nodes like 22 or 14nm, though, there are so many additional steps required that it costs a lot more to manufacture a completed wafer—not to mention additional costs for things like package-on-package (PoP) and through-silicon vias (TSV) packaging.

• Question: why is transistor count increasing but computers are becoming smaller?

Yes

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

No

- A law of math?

No

- A law of economy?

- A law of psychology?

- Question: why is transistor count increasing but computers are becoming smaller?

- Because transistors are becoming smaller

- ~1.4x smaller each dimension(1.4<sup>2</sup> ~ 2)

- Moore's Law is:

- A law of physics?

No

- A law of math?

No

- A law of economy?

Yes

- A law of psychology?

Yes

# **Today: Compute and Control Instructions**

- Different ISAs and history behind them

- What's in an ISA?

- Move operations (and addressing modes)

- Arithmetic & logical operations

- Control: Conditional branches (if... else...)

- Control: Loops (for, while)

- Control: Switch Statements (case... switch...)

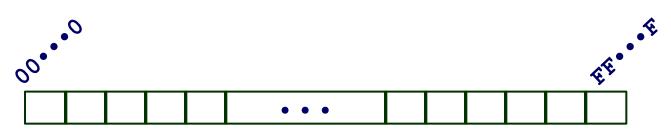

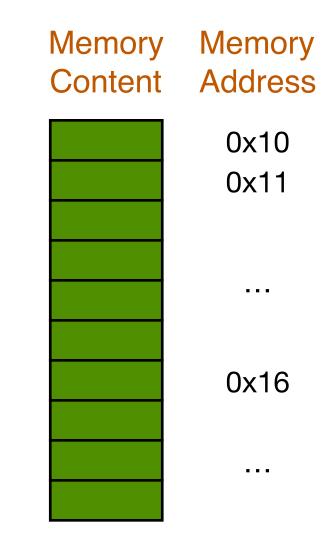

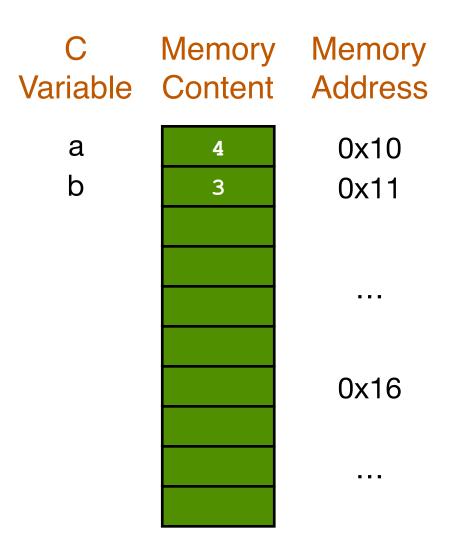

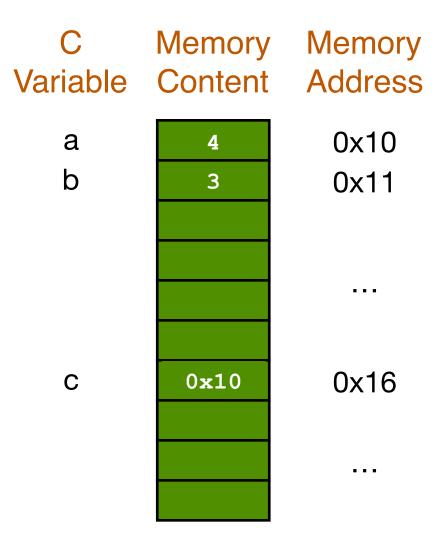

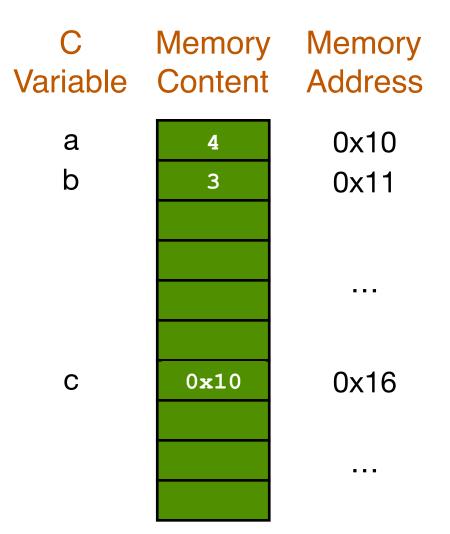

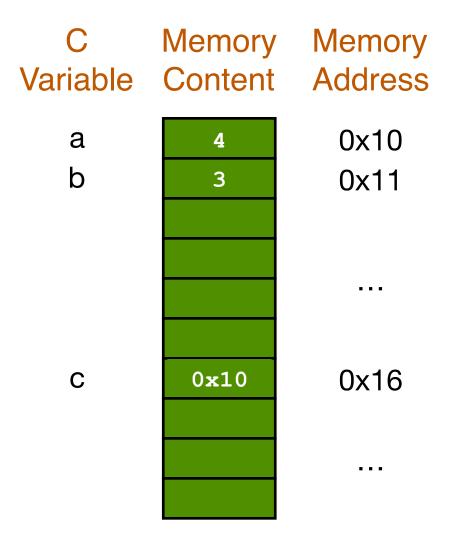

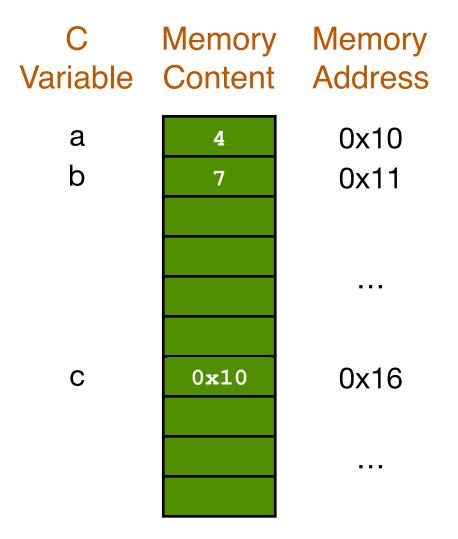

# **Byte-Oriented Memory Organization**

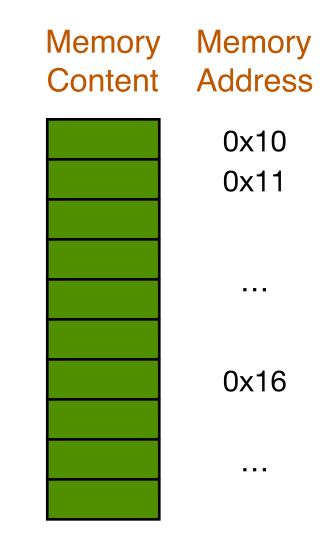

- Data in computers are stored in "memory"

- Conceptually, envision it as a very large array of bytes: byte-addressable

#### • Each byte has an address

- An address is like an index into that array

- A pointer variable is a variable that stores an address

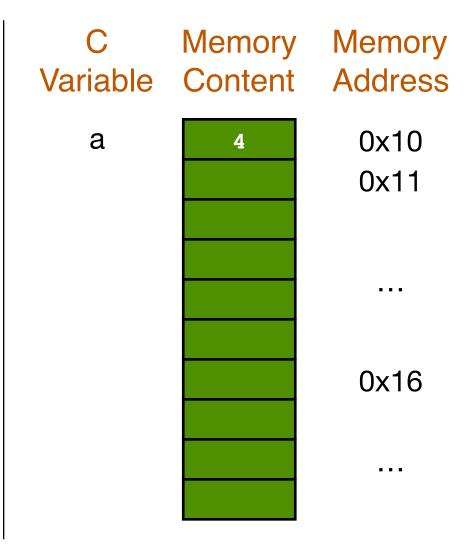

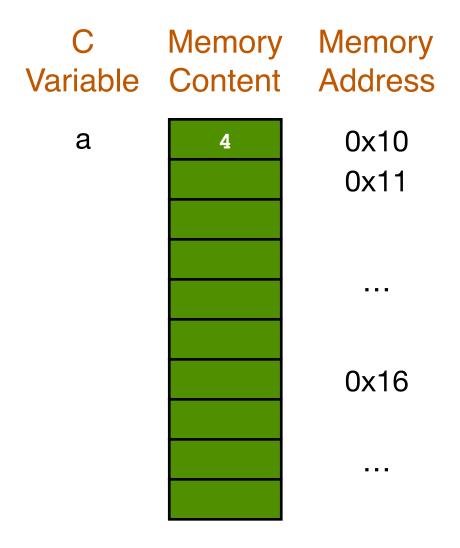

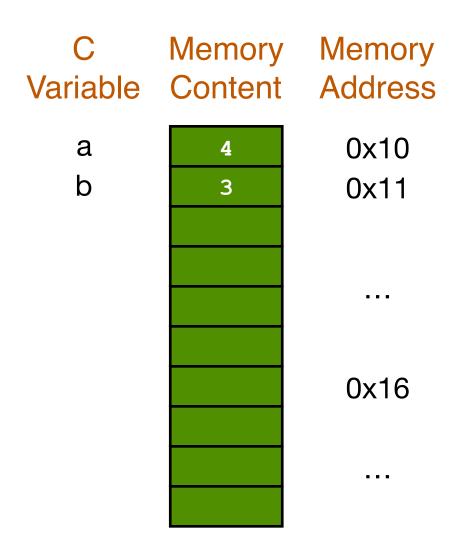

#### How Does Pointer Work in C???

- char a = 4;

- char b = 3;

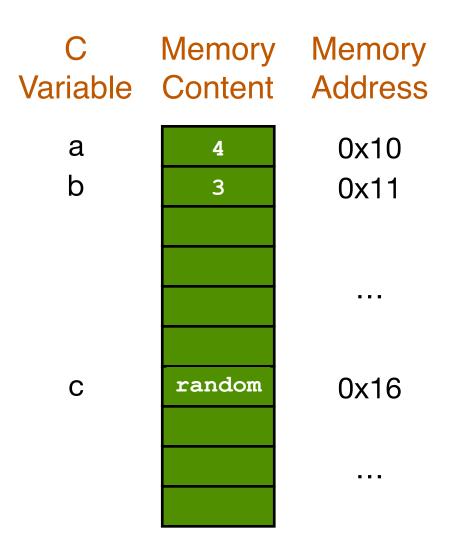

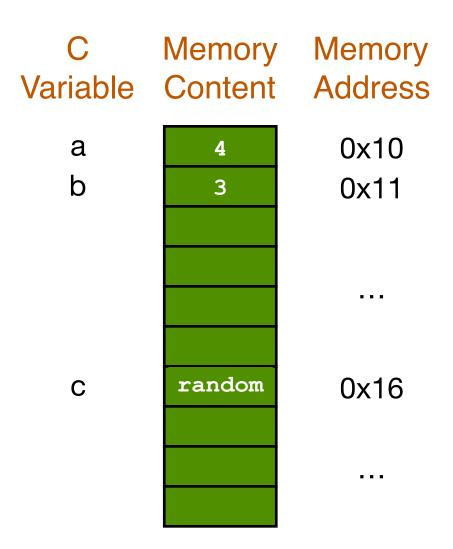

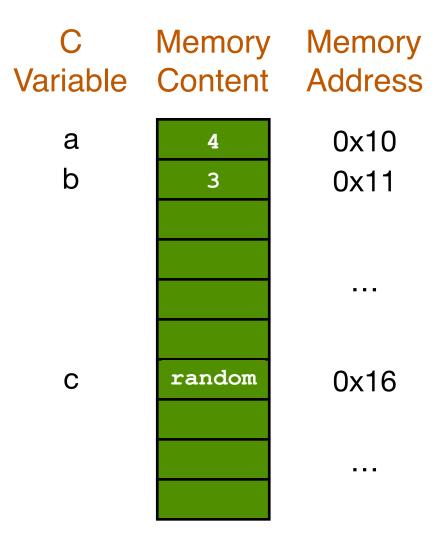

- char\* c;

- c = &a;

- b += (\*c);

#### How Does Pointer Work in C???

char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

#### How Does Pointer Work in C???

char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

| <br>char $a = 4;$ |

|-------------------|

| char $b = 3;$     |

| char* c;          |

| c = &a            |

| b += (*c);        |

|                   |

| char $a = 4;$             |  |

|---------------------------|--|

| $\rightarrow$ char b = 3; |  |

| char* c;                  |  |

| c = &a                    |  |

| b += (*c);                |  |

char a = 4;

char

$$b = 3;$$

char\* c;

$$c = \&a$$

b += (\*c);

char a = 4;

char

$$b = 3;$$

char\* c;

c = &a;

- b += (\*c);

- The content of a pointer variable is memory address.

char a = 4;

char

$$b = 3;$$

char\* c;

c = &a;

- b += (\*c);

- The content of a pointer variable is memory address.

- char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

- The content of a pointer variable is memory address.

- char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

- The content of a pointer variable is memory address.

- The '&' operator (address-of operator) returns the memory address of a variable.

- char a = 4; char b = 3; char\* c; c = &a; b += (\*c);

- The content of a pointer variable is memory address.

- The '&' operator (address-of operator) returns the memory address of a variable.

- The content of a pointer variable is memory address.

- The '&' operator (address-of operator) returns the memory address of a variable.

- The content of a pointer variable is memory address.

- The 's' operator (address-of operator) returns the memory address of a variable.

- The '\*' operator returns the content stored at the memory location pointed by the pointer variable (dereferencing)

- The content of a pointer variable is memory address.

- The '&' operator (address-of operator) returns the memory address of a variable.

- The '\*' operator returns the content stored at the memory location pointed by the pointer variable (dereferencing)

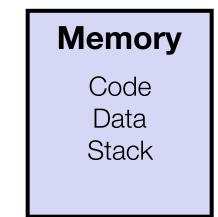

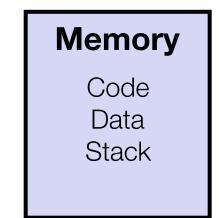

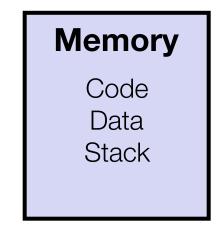

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

|  | Data |  |

|--|------|--|

|--|------|--|

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

| Data          |  |

|---------------|--|

|               |  |

| 0 <b>x</b> 53 |  |

| 0x48          |  |

| 0x89          |  |

| 0xd3          |  |

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

| Code<br>(Instructions) | Data | Stack         |

|------------------------|------|---------------|

|                        |      |               |

|                        | ÷    | 0 <b>x</b> 53 |

|                        |      | 0 <b>x</b> 48 |

|                        |      | <b>0x89</b>   |

|                        |      | 0xd3          |

| Memory        |

|---------------|

| Code          |

| Data<br>Stack |

|               |

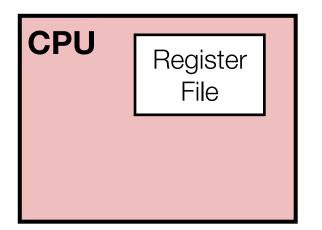

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

| 8 Bytes      | •            |

|--------------|--------------|

| %rax         | % <b>r8</b>  |

| %rbx         | % <b>r9</b>  |

| %rcx         | % <b>r10</b> |

| %rdx         | % <b>r11</b> |

| % <b>rsi</b> | 8 <b>r12</b> |

| 8rdi         | 8 <b>r13</b> |

| %rsp         | 8 <b>r14</b> |

| %rbp         | %r15         |

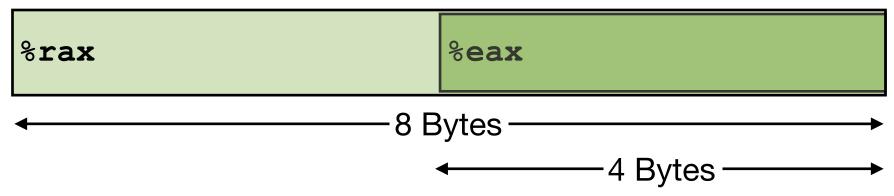

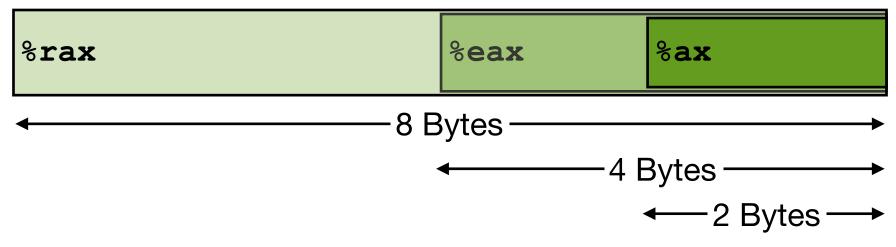

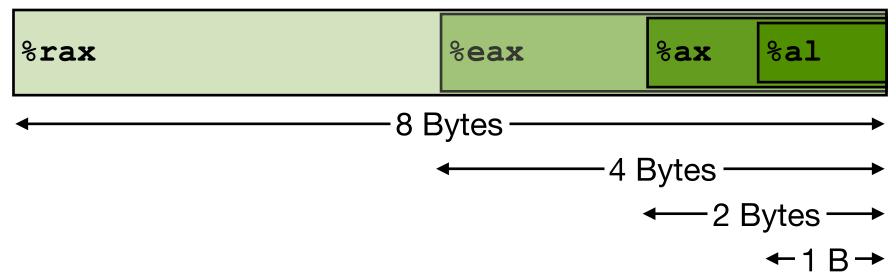

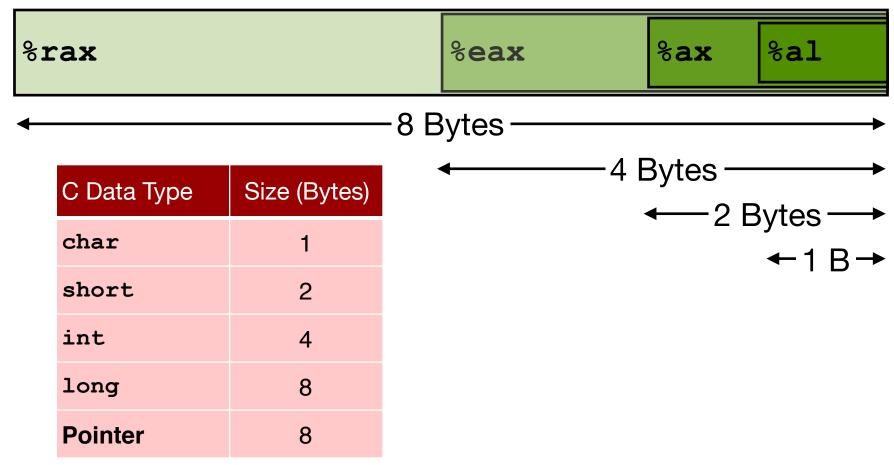

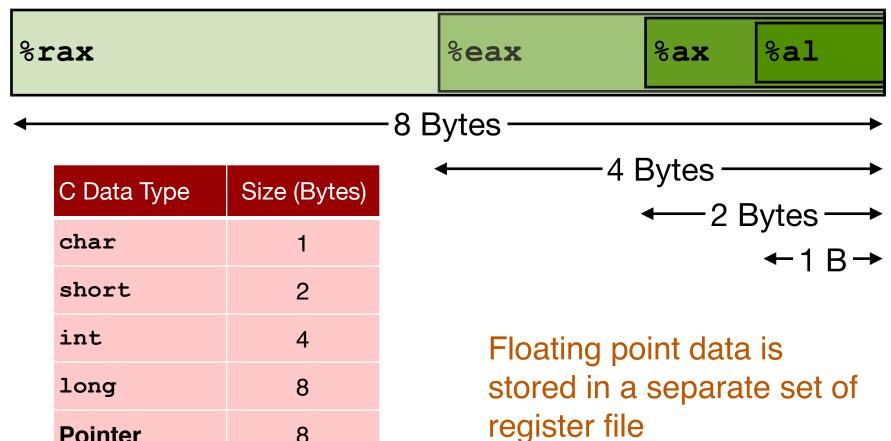

• Lower-half of each register can be independently addressed (until 1 bytes)

%rax

#### 8 Bytes

8

Pointer

| Memory       |

|--------------|

| Code<br>Data |

| Stack        |

|              |

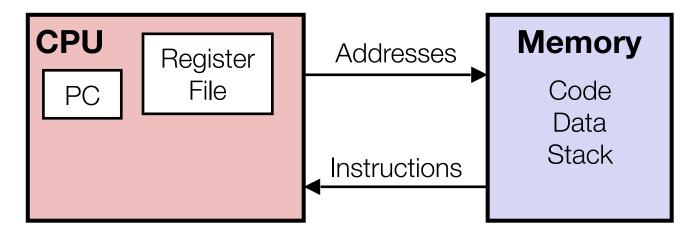

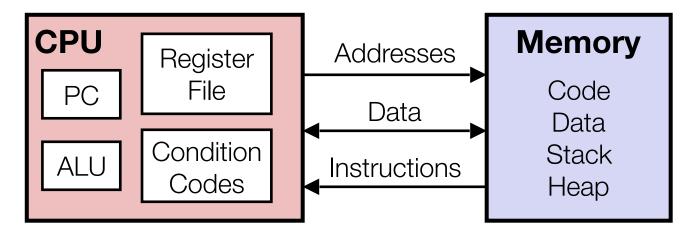

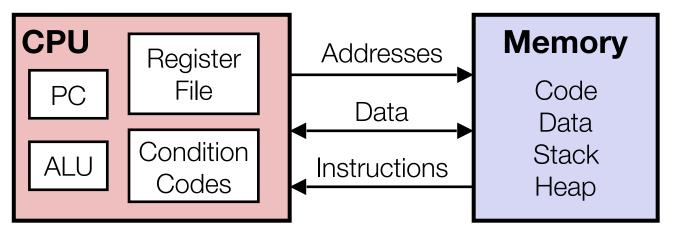

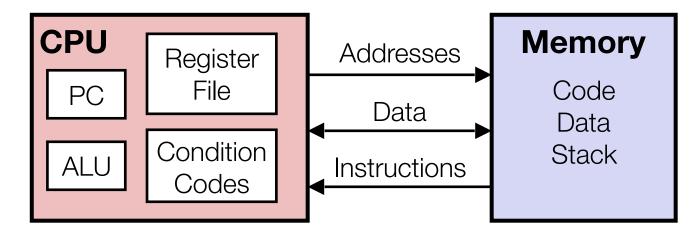

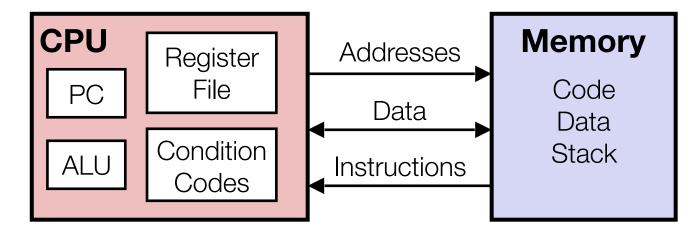

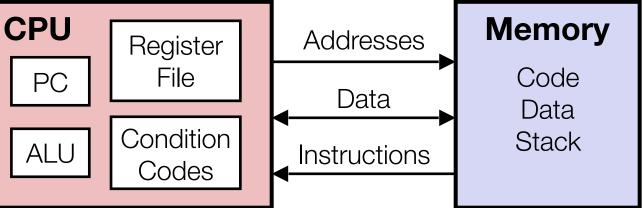

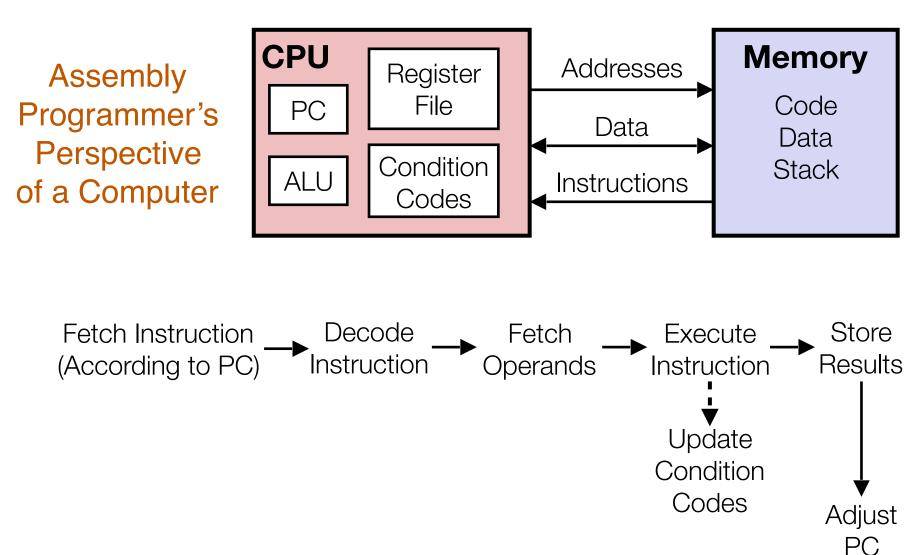

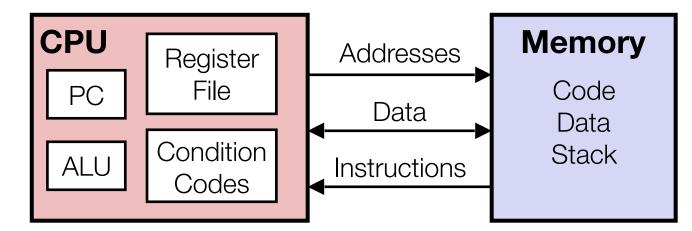

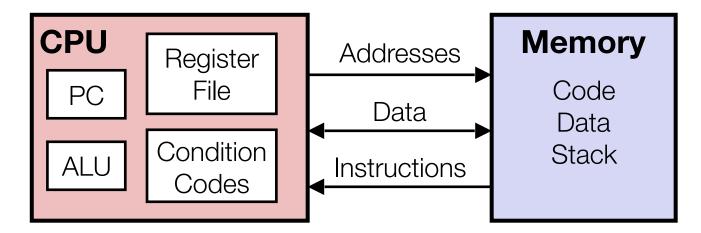

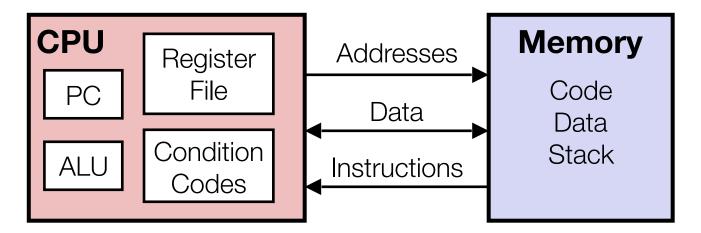

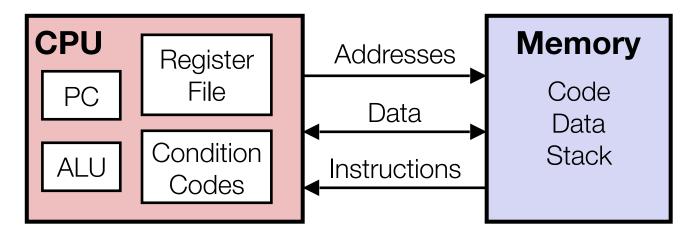

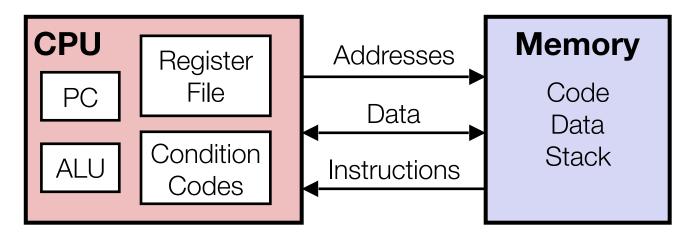

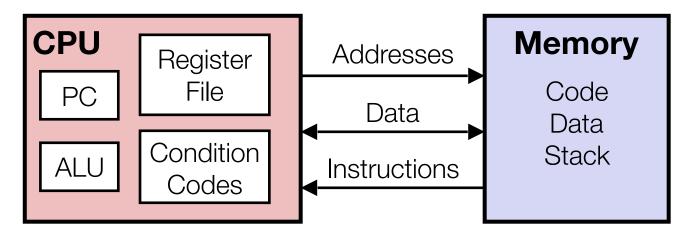

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

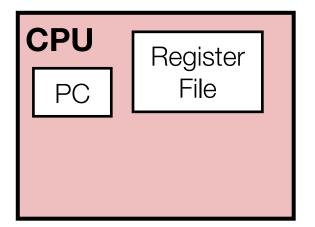

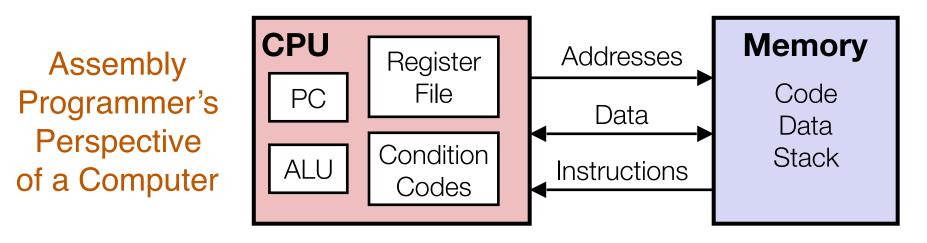

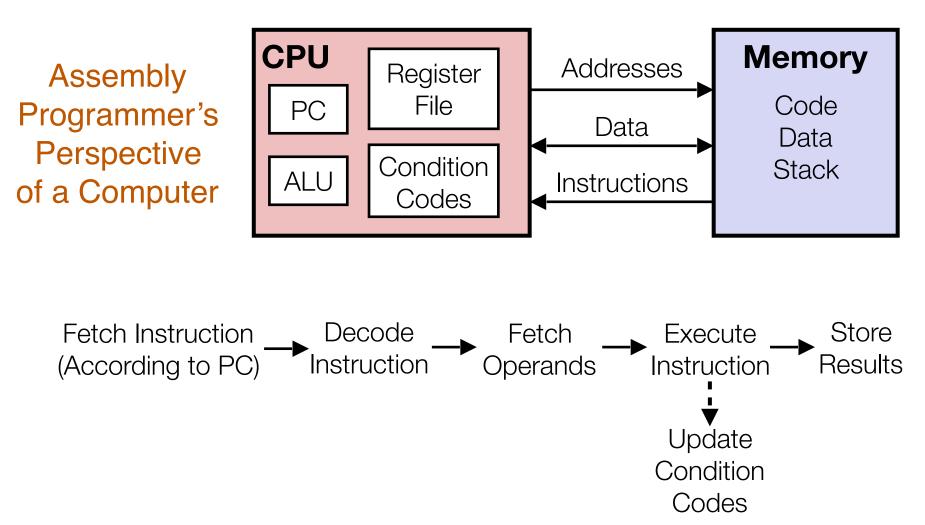

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

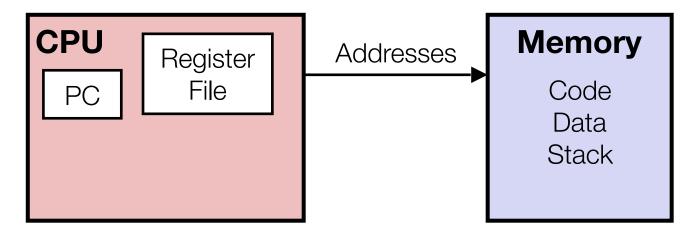

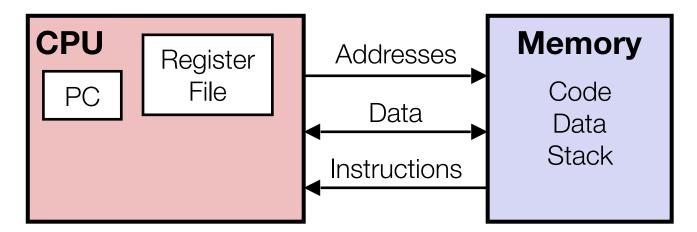

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

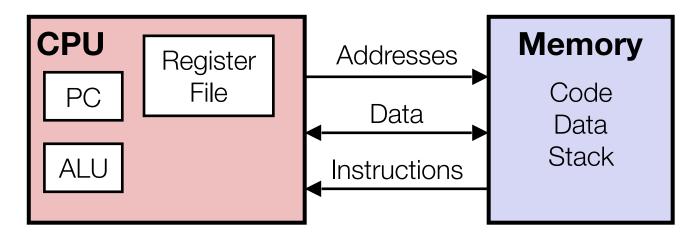

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

- Arithmetic logic unit (ALU)

- Where computation happens

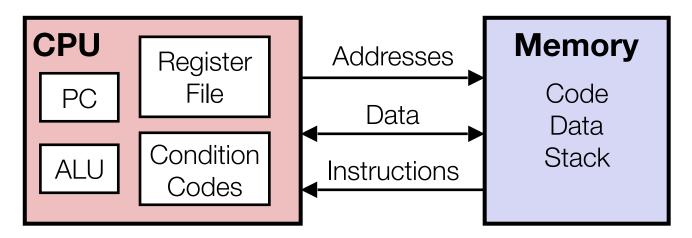

- (Byte Addressable) Memory

- Code: instructions

- Data

- Stack to support function call

- Register file

- Faster memory (e.g., 0.5 ns vs. 15 ns)

- Small memory (e.g., 128 B vs. 16 GB)

- Heavily used program data

- PC: Program counter

- A special register containing address of next instruction

- Called "RIP" in x86-64

- Arithmetic logic unit (ALU)

- Where computation happens

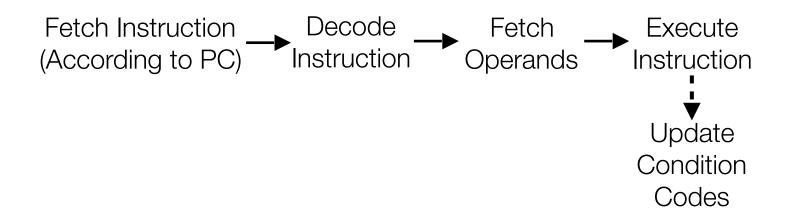

- Condition codes

- Store status information about most recent arithmetic or logical operation

- Used for conditional branch

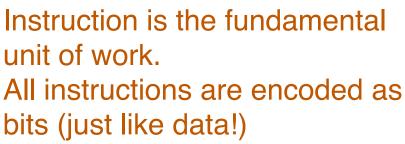

# **Assembly Program Instructions**

#### **Assembly Program Instructions**

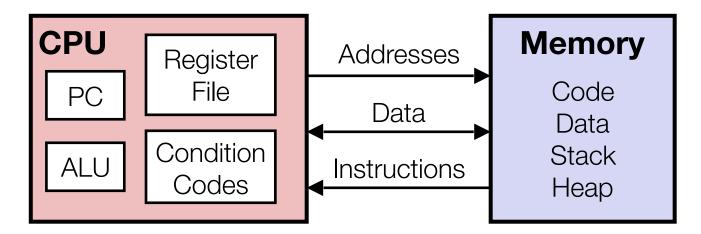

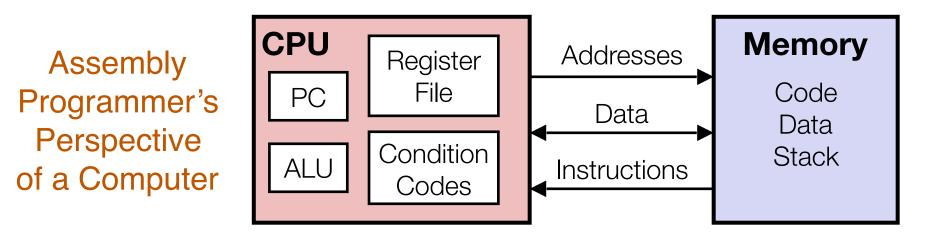

CPU **Memory** Addresses Register Assembly File Code PC **Programmer's** Data Data Perspective Condition Stack ALU Instructions of a Computer Codes Heap

- Compute Instruction: Perform arithmetics on register or memory data

- addq %eax, %ebx

- C constructs: +, -, >>, etc.

# **Assembly Program Instructions**

- Compute Instruction: Perform arithmetics on register or memory data

- addq %eax, %ebx

- C constructs: +, -, >>, etc.

- Data Movement Instruction: Transfer data between memory and register

- movq %eax, (%ebx)

# **Assembly Program Instructions**

- Compute Instruction: Perform arithmetics on register or memory data

- addq %eax, %ebx

- C constructs: +, -, >>, etc.

- Data Movement Instruction: Transfer data between memory and register

- movq %eax, (%ebx)

- Control Instruction: Alter the sequence of instructions (by changing PC)

- jmp, call

- C constructs: **if-else**, **do-while**, function call, etc.

```

C Code (sum.c)

```

```

C Code (sum.c)

```

Generated x86-64 Assembly

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | %rdx,            | % <b>rbx</b> |

| call      | plus             |              |

| movq      | <pre>%rax,</pre> | (%rbx)       |

| popq      | % <b>rbx</b>     |              |

| ret       |                  |              |

```

C Code (sum.c) Ge

long plus(long x, long y);

void sumstore(long x, long y,

long *dest)

{

long t = plus(x, y);

*dest = t;

}

```

Generated x86-64 Assembly

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | %rdx,            | % <b>rbx</b> |

| call      | plus             |              |

| movq      | <pre>%rax,</pre> | (%rbx)       |

| popq      | %rbx             |              |

| ret       |                  |              |

Obtain (on CSUG machine) with command gcc -Og -S sum.c -o sum.s

Generated x86-64 Assembly

#### sumstore:

| % <b>rbx</b> |

|--------------|

|              |

| (%rbx)       |

|              |

|              |

Generated x86-64 Assembly

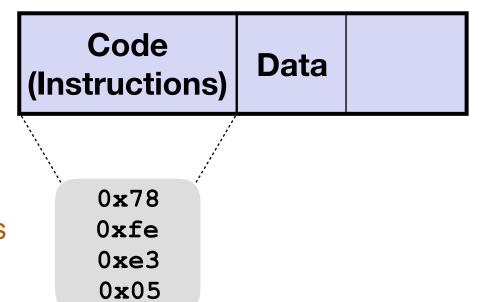

Binary Code for **sumstore**

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | %rdx,            | % <b>rbx</b> |

| call      | plus             |              |

| movq      | <pre>%rax,</pre> | (%rbx)       |

| popq      | % <b>rbx</b>     |              |

| ret       |                  |              |

Memory 0x53 0x480x89 0xd30xe8 0xf20xff 0xff 0xff 0x480x89 0x03 0x5b0xc3

Generated x86-64 Assembly

Binary Code for **sumstore**

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | %rdx,            | % <b>rbx</b> |

| call      | plus             |              |

| movq      | <pre>%rax,</pre> | (%rbx)       |

| popq      | % <b>rbx</b>     |              |

| ret       |                  |              |

| Address   | Memory       |

|-----------|--------------|

| 0x0400595 | 0x53         |

|           | 0x48<br>0x89 |

|           | 0xd3         |

|           | 0xe8         |

|           | 0xf2         |

|           | Oxff         |

|           | 0xff         |

|           | 0xff         |

|           | 0x48         |

|           | 0x89         |

|           | 0x03         |

|           | 0x5b         |

|           | 0xc3         |

19

#### Turning C into Object Code

Generated x86-64 Assembly

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | %rdx,            | % <b>rbx</b> |

| call      | plus             |              |

| movq      | <pre>%rax,</pre> | (%rbx)       |

| popq      | %rbx             |              |

| ret       |                  |              |

Obtain (on CSUG machine) with command

gcc -c sum.s -o sum.o

Binary Code for **sumstore**

| Address   | Memory        |

|-----------|---------------|

| 0x0400595 | 0 <b>x</b> 53 |

|           | <b>0x48</b>   |

|           | 0x89          |

|           | 0xd3          |

|           | 0xe8          |

|           | 0xf2          |

| nd        | 0xff          |

|           | 0xff          |

|           | 0xff          |

|           | <b>0x48</b>   |

|           | 0x89          |

|           | 0x03          |

|           | 0x5b          |

|           | 0xc3          |

19

#### Turning C into Object Code

Generated x86-64 Assembly

| sumstore: |                  |              |

|-----------|------------------|--------------|

| pushq     | % <b>rbx</b>     |              |

| movq      | %rdx,            | % <b>rbx</b> |

| call      | plus             |              |

| movq      | <pre>%rax,</pre> | (%rbx)       |

| popq      | % <b>rbx</b>     |              |

| ret       |                  |              |

Obtain (on CSUG machine) with command

gcc -c sum.s -o sum.o

- Total of 14 bytes

Instructions have variable lengths: e.g., 1, 3, or 5 bytes

- Code starts at memory address 0x0400595

Binary Code for **sumstore**

| Address   | Memory        |

|-----------|---------------|

| 0x0400595 | 0x53          |

|           | <b>0x48</b>   |

|           | 0x89          |

|           | 0xd3          |

|           | 0xe8          |

|           | 0xf2          |

| nd        | 0xff          |

|           | 0xff          |

|           | 0xff          |

|           | 0 <b>x</b> 48 |

|           | 0x89          |

|           | <b>0x03</b>   |

|           | 0x5b          |

|           | 0xc3          |

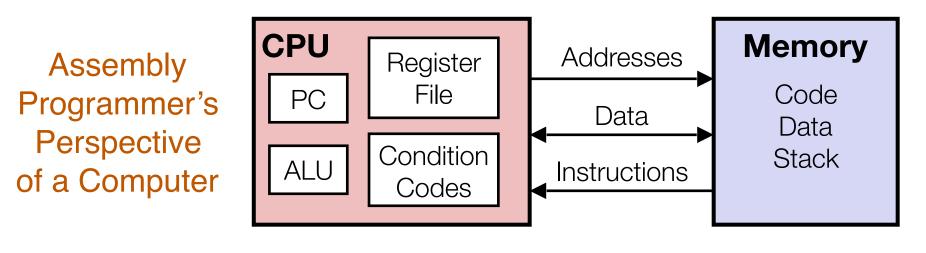

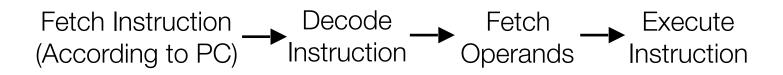

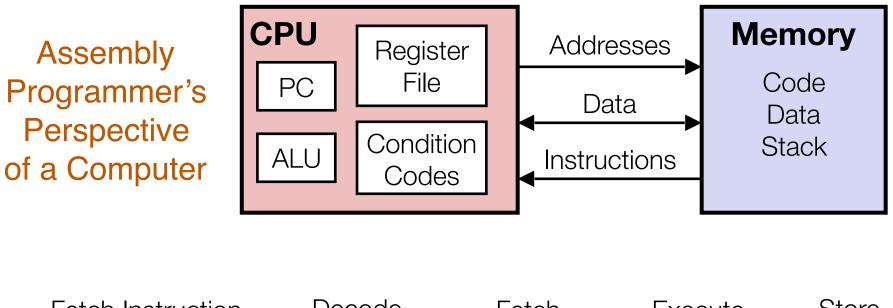

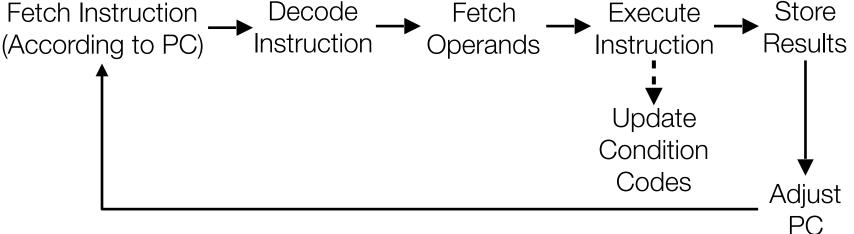

Assembly Programmer's Perspective of a Computer

Fetch Instruction (According to PC)

Assembly Programmer's Perspective of a Computer

Fetch Instruction (According to PC)

0x4801d8

Assembly Programmer's Perspective of a Computer

Fetch Instruction — Decode (According to PC) — Instruction

addq %rax,(%rbx)

# **Today: Compute and Control Instructions**

- Different ISAs and history behind them

- What's in an ISA?

- Move operations (and addressing modes)

- Arithmetic & logical operations

- Control: Conditional branches (if... else...)

- Control: Loops (for, while)

- Control: Switch Statements (case... switch...)

Assembly Programmer's Perspective of a Computer

• Initially all data is in the memory

- Initially all data is in the memory

- But memory is slow: e.g., 15 ns for each access

- Initially all data is in the memory

- But memory is slow: e.g., 15 ns for each access

- Idea: move the frequently used data to a faster memory

- Initially all data is in the memory

- But memory is slow: e.g., 15 ns for each access

- Idea: move the frequently used data to a faster memory

- Register file is faster (but much smaller) memory: e.g., 0.5 ns

- Initially all data is in the memory

- But memory is slow: e.g., 15 ns for each access

- Idea: move the frequently used data to a faster memory

- Register file is faster (but much smaller) memory: e.g., 0.5 ns

- There are other kinds of faster memory that we will talk about later

- Initially all data is in the memory

- But memory is slow: e.g., 15 ns for each access

- Idea: move the frequently used data to a faster memory

- Register file is faster (but much smaller) memory: e.g., 0.5 ns

- There are other kinds of faster memory that we will talk about later

- Key: register file is programmer visible, i.e., you could use instructions to explicitly move data between memory and register file.

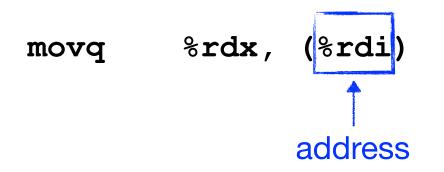

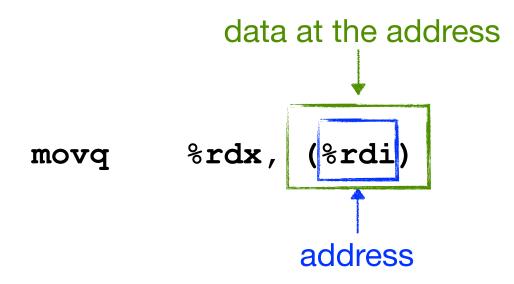

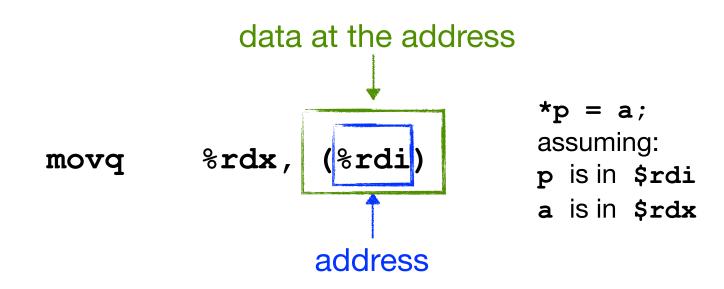

movq %rdx, (%rdi)

#### • Semantics:

- Move (really, copy) data in register %rdx to memory location whose address is the value stored in %rdi

- Pointer dereferencing

- Semantics:

- Move (really, copy) data in register %rdx to memory location whose address is the value stored in %rdi

- Pointer dereferencing

- Semantics:

- Move (really, copy) data in register %rdx to memory location whose address is the value stored in %rdi

- Pointer dereferencing

#### Semantics:

- Move (really, copy) data in register %rdx to memory location whose address is the value stored in %rdi

- Pointer dereferencing